A Look At The Ice Lake Thunderbolt 3 Integration

Although the high-performance Sunny Cove cores and Gen 11 Graphics of Intel’s new Ice Lake SoC get all the attention, perhaps just as interesting, is the all-new Thunderbolt 3 IO subsystem. “Looking back at our history, we have not gone through an integration of this size since the integration of the graphics on Sandy Bridge,†said Ophir Edlis, Ice Lake SoC lead architect.

At 40 Gb/s, Thunderbolt 3 is currently one of fastest general-purpose I/O available in the PC ecosystem. The protocol itself is quite versatile. It can double up as x4 PCIe Gen 3.0, USB 3.1, and DisplayPort 1.2. Manufacturers can also support charging the system using the USB Power Delivery (USB-PD) specs. As far as display support goes, it can drive up to two external 4K displays at 60 Hz. So any existing peripheral is essentially supported out of the box through Thunderbolt.

Thunderbolt is a tunneling-based architecture. It’s a single interface that combines all the protocols we listed above. The key feature of TB3 is dynamic allocation. Through a quality of service mechanism, the device can decide which protocol, either DP or PCIe, gets what kind of priority. In other words, the total bandwidth can be dynamically allocated on-demand depending on the kind of peripherals currently being connected and on the behavior of the currently running workload.

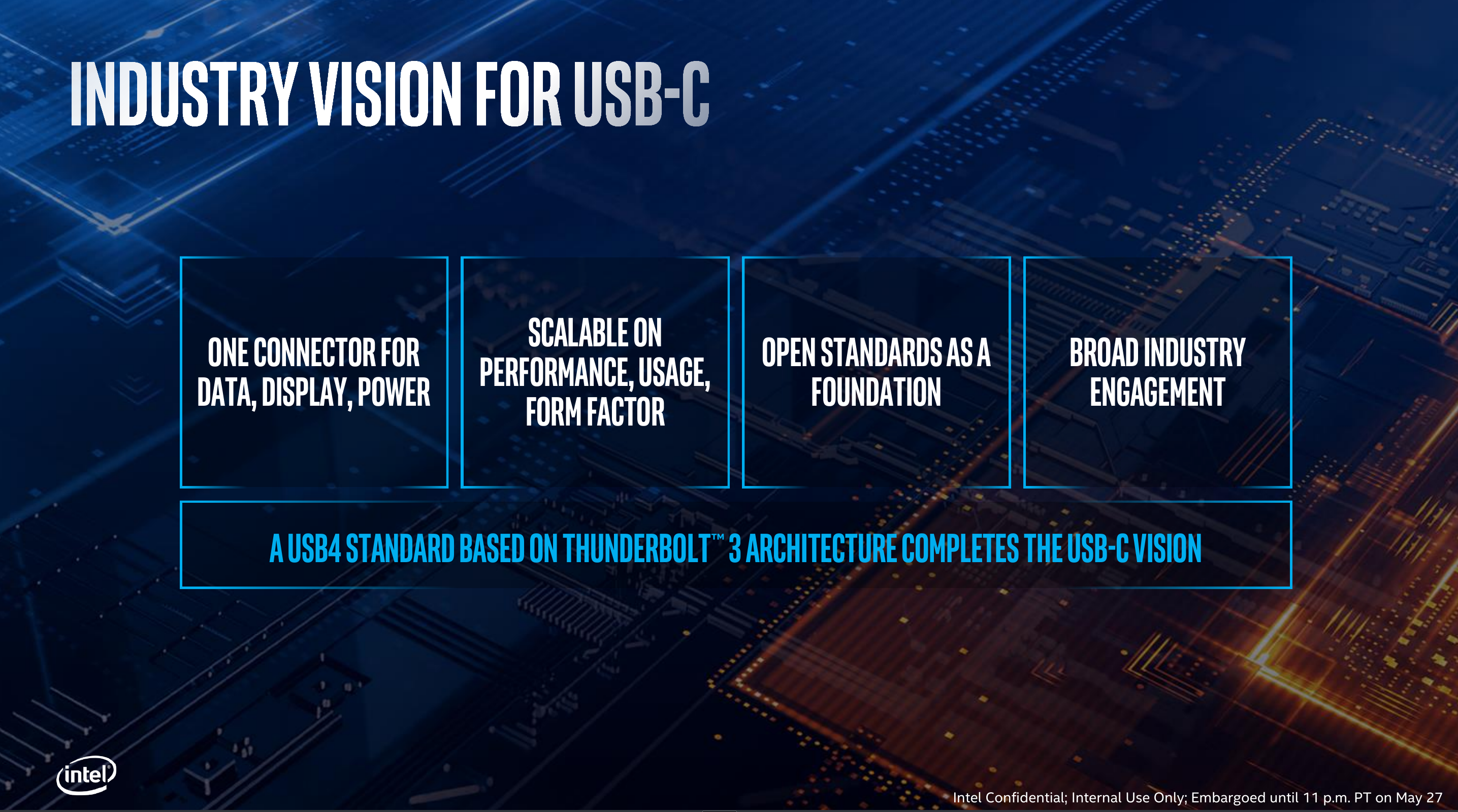

Earlier this year, Intel contributed the Thunderbolt 3 protocol to USB 4. The move was an effort by Intel to accelerate the adoption of Thunderbolt 3. Intel says that it believes Ice Lake is actually already USB 4-compliant, however, it cannot certify their source side as compliant until the sync side is made available for testing. Going forward, both brands will be used. Intel considers USB 4 a spec-driven approach whereas Thunderbolt remains a holistic solution which includes validation, verification, and comes with certain guarantees.

Thunderbolt 3 Integration – Outside Ice Lake

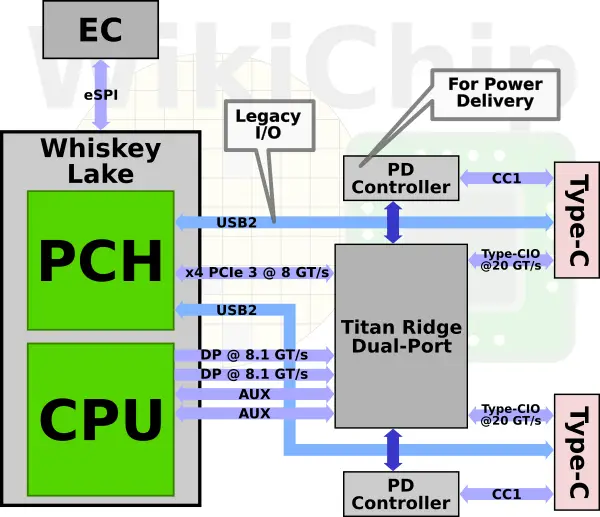

In existing 8th Generation processors, in order to provide Thunderbolt 3 capabilities, OEMs have to use the Titan Ridge controller. This is a discrete Thunderbolt 3 chip designed by Intel. Titan Ridge comes with support for either one or two dedicated Tb3 ports. In this configuration, Titan Ridge was connected to both the CPU itself and the chipset. The chipset was connected over four PCIe Gen 3 lanes. The CPU had two DisplayPort connections. Each of those passed over four PCIe Gen 3 lanes. In order to offer legacy I/O support, a direct USB 2.0 link from the PCH went to the port. For charging capabilities, the port was also connected directly to a Power Deliver (PD) controller. All in all, the Titan Ridge controller alone required a total of seventeen lanes operating at around 8 GT/s.

By the way, due to the complexity involved, most devices today only have the Thunderbolt 3 ports on that one side with the Titan Ridge controller. The diagram below shows just one of those sides, using a dual-port controller.

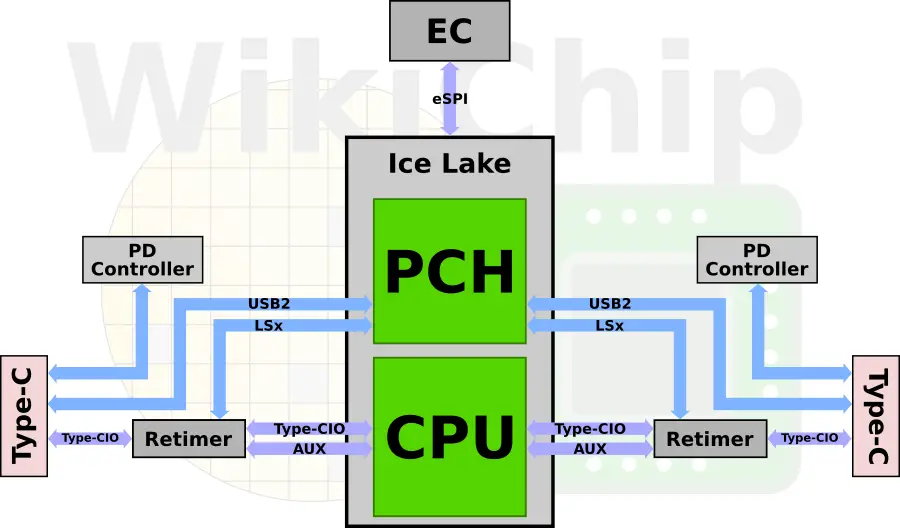

With Ice Lake, the circuit has been simplified a fair amount. The simplification manifests itself in a number of ways. The biggest change comes from the fact that most of the Titan Ridge logic has been integrated into the Ice Lake SoC itself, reducing board space, routing, and the overall bill of materials. Instead of the seventeen PCIe lanes from the prior generation, Ice Lake exposes just eight lanes – four lanes to each retimer which drive the signals to the connectors. So now there is a total of just eight lanes operating at 20 GT/s instead of seventeen lanes operating at 8 GT/s. The reduction of lanes, along with their associated components such as the buffers, reduces the overall power consumption of the system. “We see a reduction of up to 300 mW per port when the port is fully utilized,” Edlis said. When considering that the latest Thunderbolt 3 controller, such as the JHL7440, has a TDP of 2.4 W, that’s a pretty sizeable saving in power. “By reducing the power with this integration, we can allocate more power to the CPU, even under full utilization,” Edlis added.

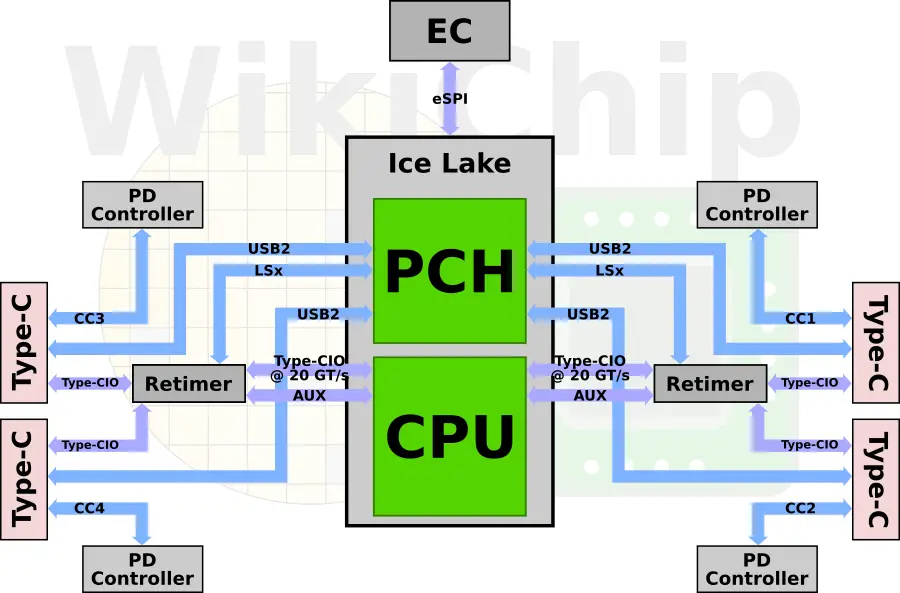

As mentioned earlier, due to the discrete Titan Ridge controller, on most current laptops, the Thunderbolt 3 port is only offered on one side of the device; normally on the side located near the controller itself. The other side usually features a legacy connector of some sort such as a USB 2.0. With Ice Lake, the direct Thunderbolt lanes that go to each retimer are easily exposed to both sides of the device, meaning, at least in theory, OEMs should have no problem offering symmetrical connections on both sides of the device.

By the way, like Titan Ridge, each retimer supports two ports. The retimers themselves are still only sold by Intel but they are a fraction of the size, so there is some board space saving advantage as well. Therefore, actually, the diagram above is almost identical when offering support for up to four Thunderbolt 3 ports, twice as many as most Titan Ridge-based designs. For full support, those additional ports just need a new dedicated USB 2 connection to the PCH, and in order to also offer charging capabilities through that port, you also need a PD controller. A good premium-design laptop should, therefore, be able to have up to four Thunderbolt ports – each supporting everything from power delivery to the legacy I/O to the latest high-speed interfaces such as DisplayPort and USB 3.1.

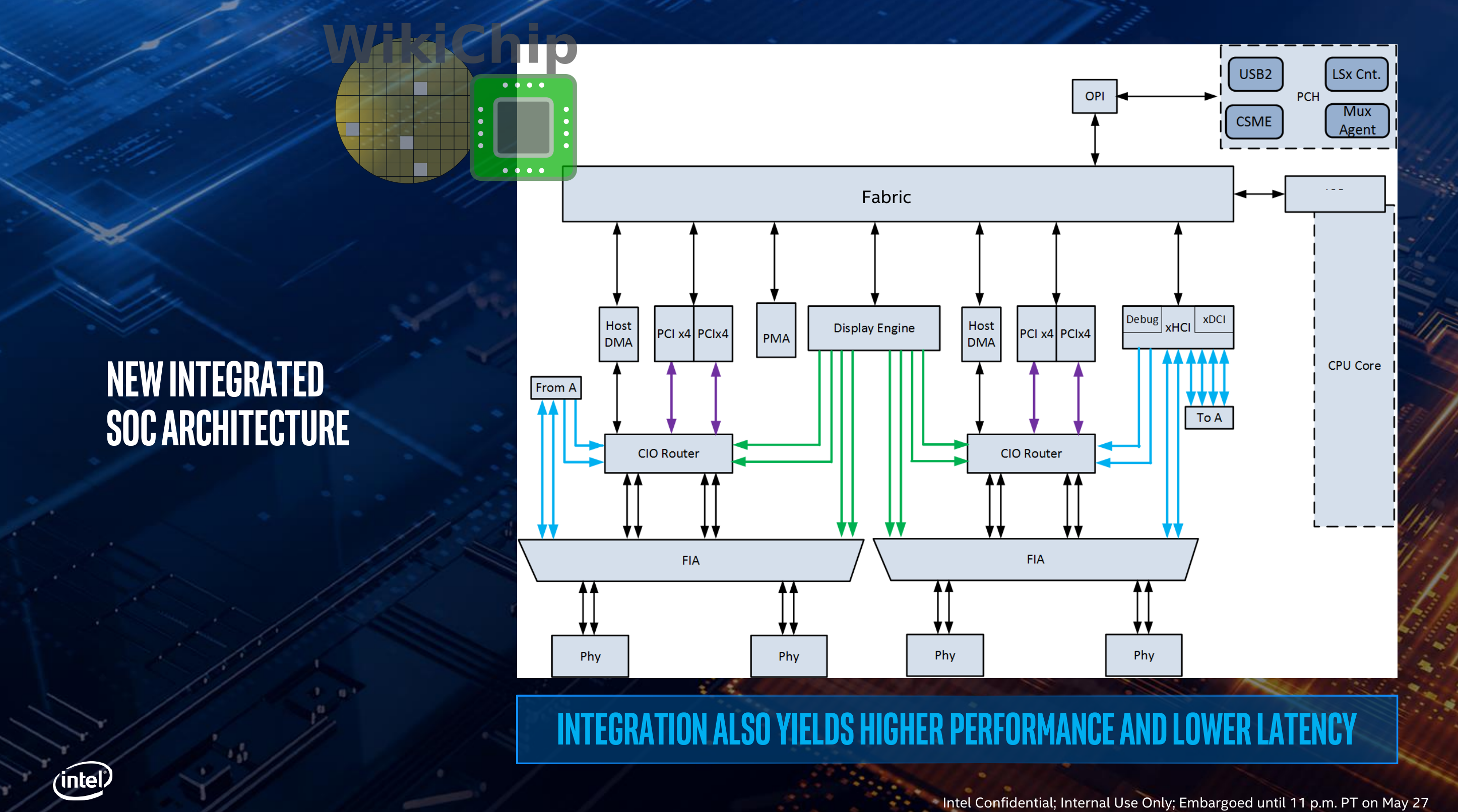

Thunderbolt 3 Integration – Inside Ice Lake

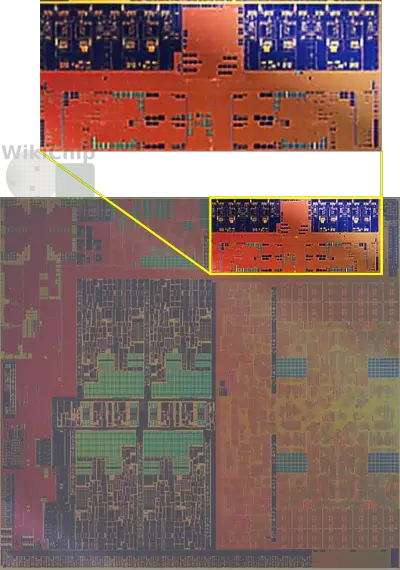

Before delving into the details, it’s worth looking at the physical layout of the SoC. The new Thunderbolt 3 I/O subsystem is located at the upper right corner of the die when positioning the memory interface at the bottom. It is situated right next to the Display Engine for latency reasons. By our estimates, this subsystem makes up roughly 8.8% of the entire silicon area of the SoC. This is a pretty big chunk of silicon when you consider that roughly 1.7 Sunny Cove cores could fit in that space.

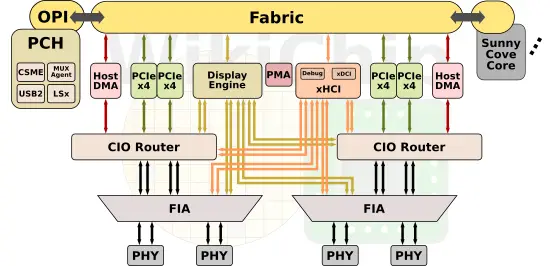

Ice Lake standardized the way new IPs are connected to the fabric – it’s what enables some of the new integrations such as the Gaussian Neural Accelerator, but it also connects to the Host DMA, the PCIe Controllers, the Display Engine, and the eXtensible Host Controller Interface (xHCI) USB controller. Ice Lake contains two modular FIAs, each one connect to a pair of Type-C ports for a total of four ports. The FIA can multiplex between a standard USB Type-C connector and a Thunderbolt connector.

Each FIA is connected to the USB controller, Display Engine, and the CIO Router. The CIO Router is the actual Thunderbolt router and it can be thought of as a display engine as well. Ice Lake has a total of four PCIe controllers coming from four root complexes. Two PCIe controllers go to each of the CIOs. Previously, there was just a single PCIe controller going to the Titan Ridge controller, so there was effectively one PCIe controller for both ports. This means that compared to the prior generation, each port now effectively has double the bandwidth.

Overall, Ice Lake brings I/O improvements to mobile devices through a tighter integration of Thunderbolt 3 which should help translate to wider adaptation, along with modest performance, power, and area improvement.

WikiChip derived articles: Intel Ice Lake § Thunderbolt IO subsystem.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–