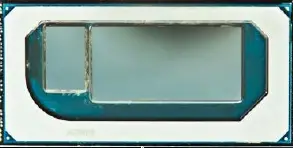

Arm Launches the Cortex-M55 and Its MicroNPU Companion, the Ethos-U55

Arm launches two new IPs for deeply-embedded AI: the Cortex-M55 with the new M-Profile Vector Extension (Helium), and the Ethos-U55, an ultra-low-power dedicated NPU for embedded applications.

Read more