Intel Introduces 2nd Gen Neuromorphic Research Chip: Loihi 2 on Intel 4 EUV Process

One area of focus within Intel Labs is neuromorphic computing. Intel’s Neuromorphic Computing Lab (NCL) major effort in the field of neuromorphic chips started with the introduction of the Loihi chip in 2018. The chip – which was intended for research only – incorporated a large number of features with the intent of covering a broad enough spectrum of research directions. Future chips would eliminate unnecessary features and hone down on the more useful ones.

Introducing Loihi 2

Today Intel is introducing its second-generation follow-up chip: Loihi 2. The chip brings advances on several fronts. Although it remains a research chip, Loihi 2 is more refined feature-wise bringing it a step close towards commercialization. The architecture was significantly enhanced based on feedback from their original chip. Loihi 2 is also fabricated on Intel 4 process (formerly Intel 7nm). This makes it not only Intel’s first public Intel 4-based chip, but it’s also the company’s first public chip to utilize extreme ultraviolet lithography.

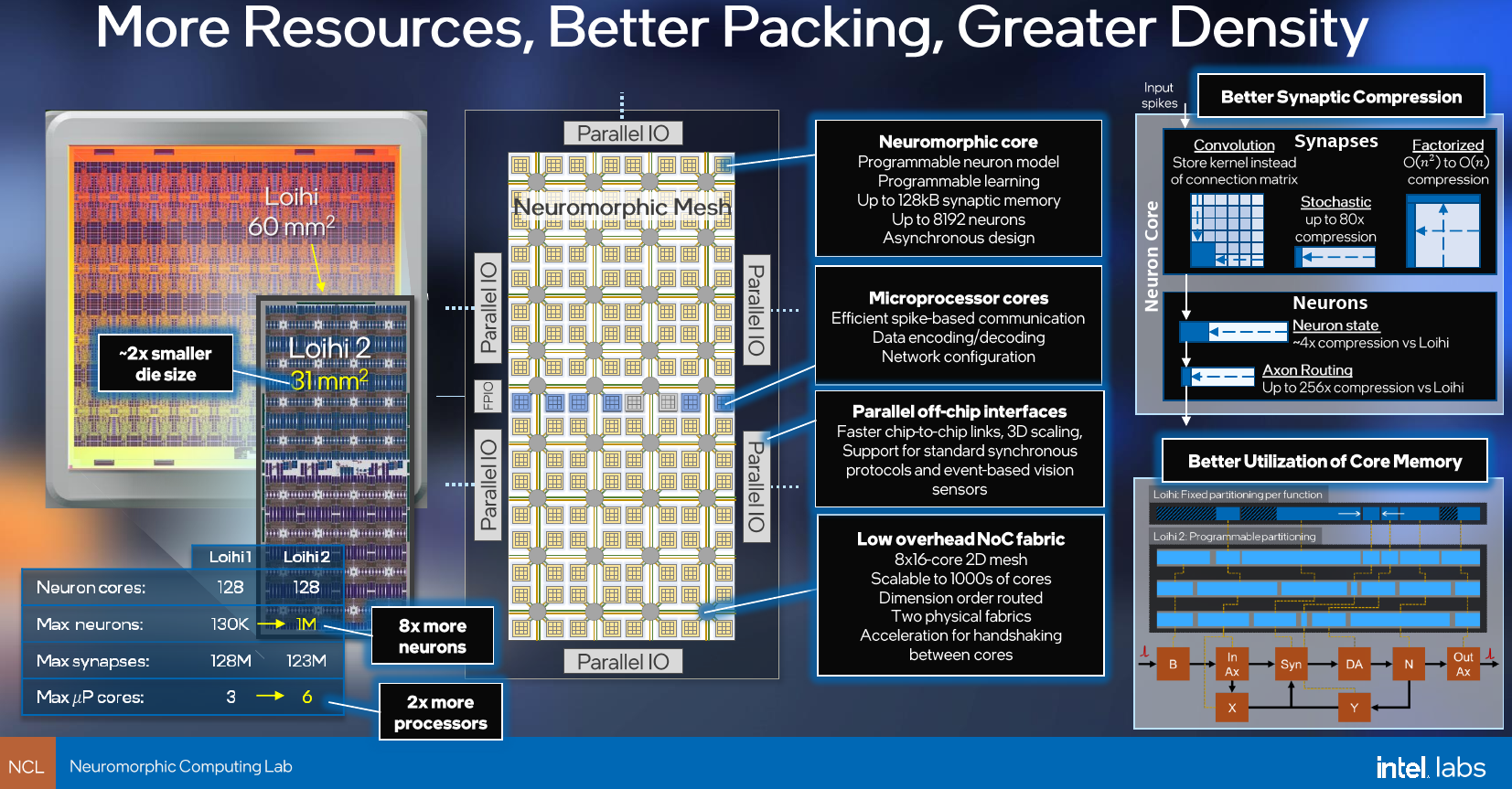

Whereas Loihi was a 14-nanometer chip, Loihi 2 is fabricated on a pre-production version of Intel 4 EUV process. With 2.3 billion transistors (200 million more than Loihi), the new chip is 31 mm² or roughly half the size of the original Loihi chip. Much of the transistor budget was juggle around. Loihi 2 builds on Loihi. For that reason, it is architecturally similar at a high level – maintaining the mesh of 128 neuron cores. Intel did revamp the entire communication model between neurons. Loihi focused on spiking neural networks. Whereas previously Loihi only supported spiking pulses (1-bit synapse format), Loihi 2 generalized those spikes with integer-valued payloads where desired. Although that slightly decreases the performance efficiency when used, the ability to communicate with richer 32-bit messages is said to allow for better precision in certain algorithms. To help with this, Intel redesigned the neurons, incorporating a programmable pipeline in each core. Control flow, comparison, and common arithmetic instructions are now supported in the new pipeline.

Since the transistor budge is largely the same, some things had to give. The total number of synapses per die was slightly reduced from 128 million to 120 million. Additionally, the memory allocated per core was reduced to 192 KiB. Instead, Intel used those transistors to significantly increase the neuron density of the die. Whereas Loihi had 128,000 neurons, Loihi 2 integrates a million. When compared to IBM TrueNorth, Loihi 2 has the same amount of neurons as TrueNorth but half the number of synapses (IBM had 256 million). But this comparison is not exactly apples-to-apples given that it used binary spikes (like Loihi 1) and the online learning capabilities differ.

One of the other changes Intel said it has made in Loihi 2 is the low-level circuit optimizations. With significant effort in redesigning and optimizing the pipeline, Intel claims Loihi 2 achieves over 2x processing speed improvement for neuron state updates, 5x faster synaptic operations, and 10x faster spike generations. All in all, Intel says that Loihi 2 supports chip-wide minimum time steps lower than 200ns.

There are several other major changes in Loihi 2. Loihi integrated three Lakemont cores. Those are ultra-tiny Pentium-class x86 cores that can do any management and control related tasks, programmed through standard C or Python code. On Loihi 2, Intel doubled the amount to six embedded cores to improve application performance that was previously bottlenecked by the three general cores.

To improve the ability to scale up Loihi 2, Intel beefed up the chip I/O capabilities as well. In addition to being able to extend to multiple chips to the north/south, east/west, Loihi 2 supports Radix-6 mesh routing, extending in 3D. This change was designed to allow for chips to be stacked back-to-back on a PCB and enable easier routing. Loihi 2 also added new standard interfaces for easier system integration. There is now 1000BASE-KX, 2500BASE-KX, and 10GBase-KR Ethernet interface support. Along with those interfaces, Intel also added configurable hardware-accelerated data encoders that can directly perform encoding/decoding from/to input data and spike messages.

Systems

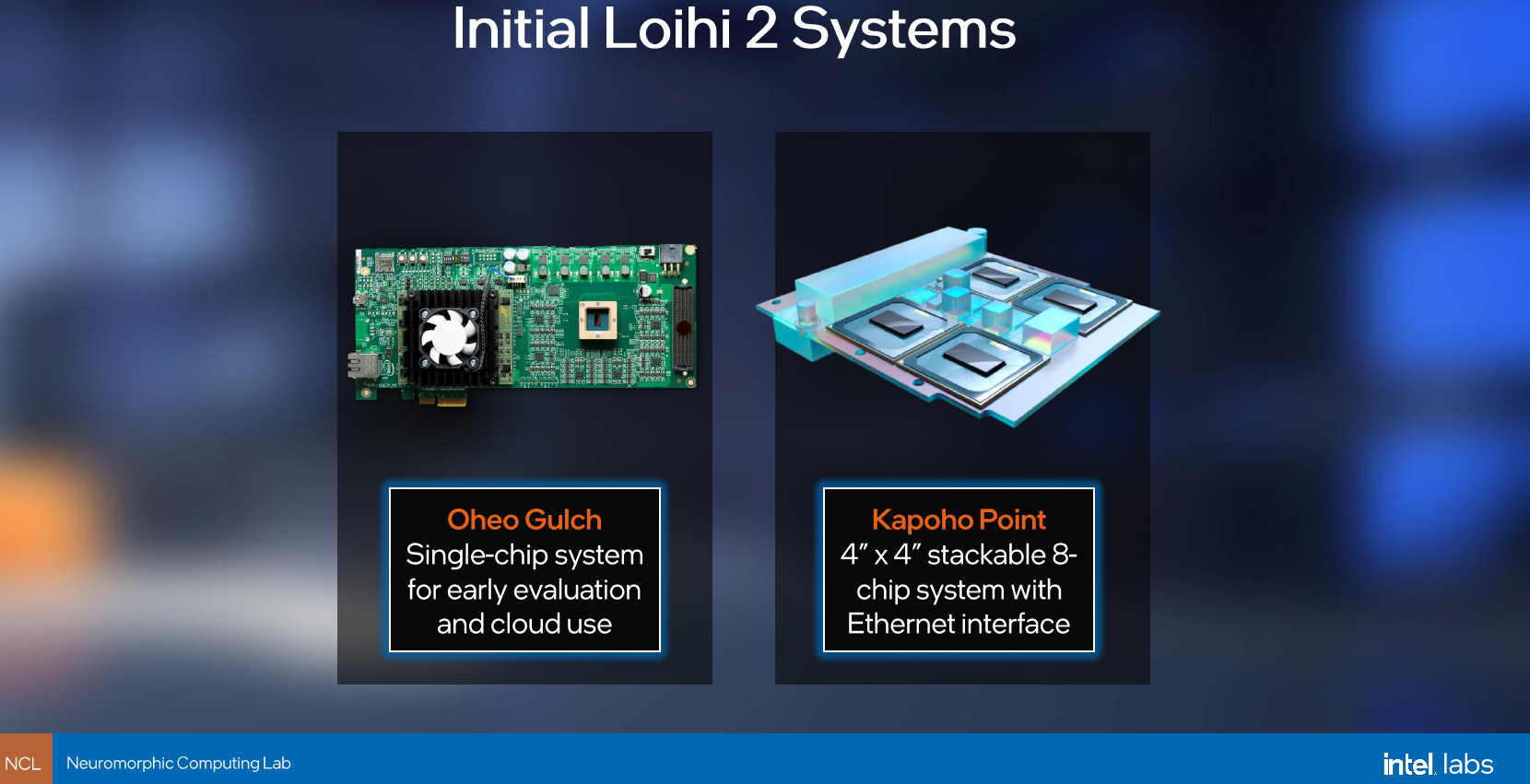

Along with Loihi 2, Intel is announcing two initial systems. The first one is a single-chip system called Oheo Gulch aimed at early research evaluations. That system has an Arria 10 FPGA that interfaces with the socketed Loihi 2 chip. Intel is offering this system today via their Neuromorphic Research cloud to Intel Neuromorphic Research Community (INRC) members. A larger system called Kapoho Point will be introduced later this year. Kapoho Point is an 8-Loihi 2 system packaged as a 4×4 (double-sided) stackable board with an Ethernet interface.

With Kapoho Point and 8 chips, this system has a total of 8 million neurons along with almost a billion synapses. Kapoho Point is tiny in a roughly 4-inch by 4-inch board. That’s a pretty large density improvement. To get this amount of neurons and synapses on the prior chip, you’d have to get one of the larger Loihi-based systems such as the Pohoiki Beach which had 64 chips and 8 million neurons in a very large server chassis.

As with Loihi, we expect larger Loihi 2-based systems to emerge for research purposes later on.

Lava

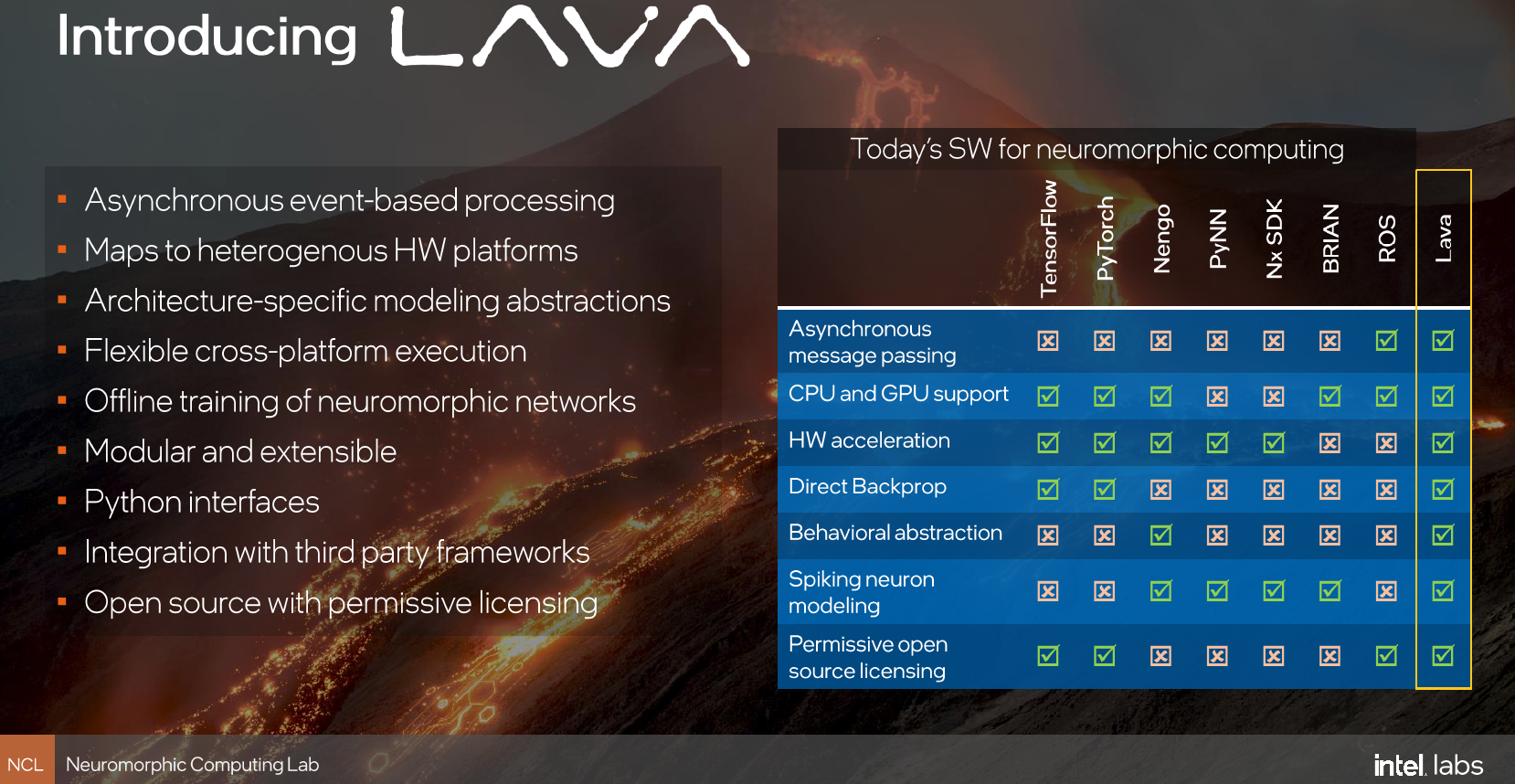

Loihi 2 is coming with a new, open-source software framework called Lava. When Intel first introduced Loihi, they also introduced the Nx SDK Software Architecture. The Nx framework included the NxCore and NxRunTime along with the NxCompiler on top of which runs the NxNet API along with various computation modules. The trouble with that framework is that it offered a low-level abstraction, making software development rather difficult. This is where Lava attempts to fit in. Lava offers a platform-agnostic (specifically designed not tied to Loihi architecture), open-source framework for neuro-inspired applications. Catering to the broader neuromorphic community, Lava offers an abstracted programming model that can map to the underlying hardware such as Loihi.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–