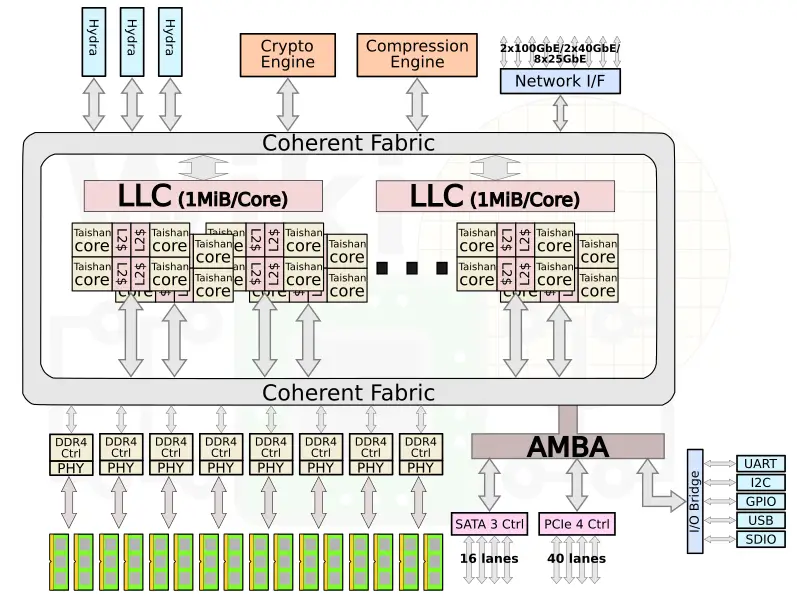

TSMC 7nm HD and HP Cells, 2nd Gen 7nm, And The Snapdragon 855 DTCO

Update and analysis of TSMC 7-nanometer node low-power and high-performance cells, 2nd generation 7nm, and the design technology co-optimization (DTCO) effort that went into the Snapdragon 855 SoC.

Read more