Intel Launches New Core X Enthusiasts Microprocessors; Doubles The Perf-Per-Dollar

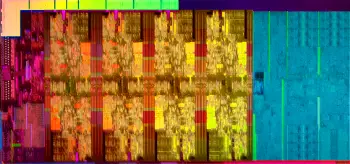

Intel launches new 10000 series Core X processors for enthusiasts with up to 18 cores and with double the performance per dollar compared to the last generation.

Read more