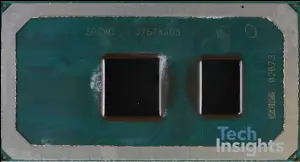

A Look at Intel’s 10nm Std Cell as TechInsights Reports on the i3-8121U, finds Ruthenium

WikiChip takes another look at Intel’s 10-nanometer standard cell design and discusses TechInsights findings of the first 10nm-based chip, the i3-8121U.

Read more