Intel Launches Stratix 10 GX 10M; 10M LEs, Two Massive Interconnected Dies

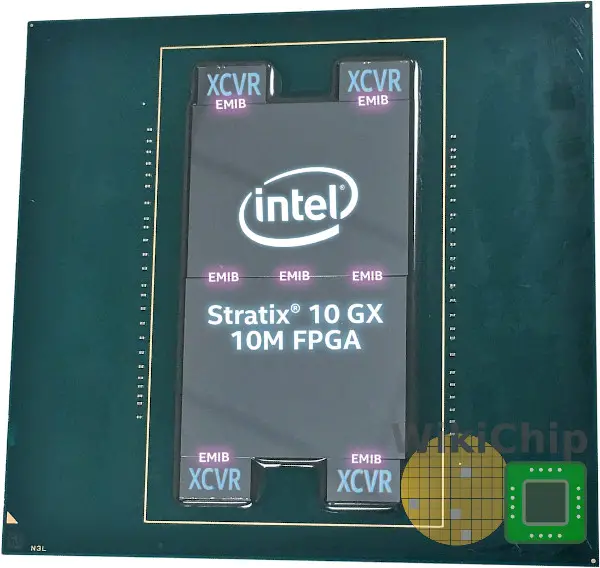

Intel launches the industry’s highest-capacity FPGA; 10-million LEs comprising two large FPGA dies interconnected using the company’s 2.5D EMIB packaging technology.

Read more