ISSCC 2018: Intel’s Skylake-SP Mesh and Floorplan

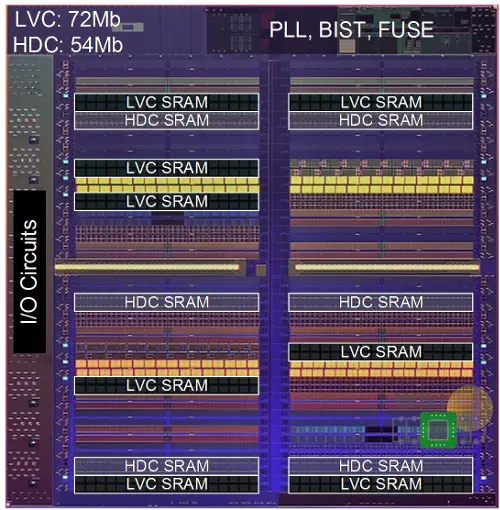

At ISSCC 2018 Intel gave us some more interesting architectural details of their latest Skylake server microprocessors which brought a new mesh interconnect, a new cache hierarchy, and wider vector operations among a large array of other enhancements.

Read more