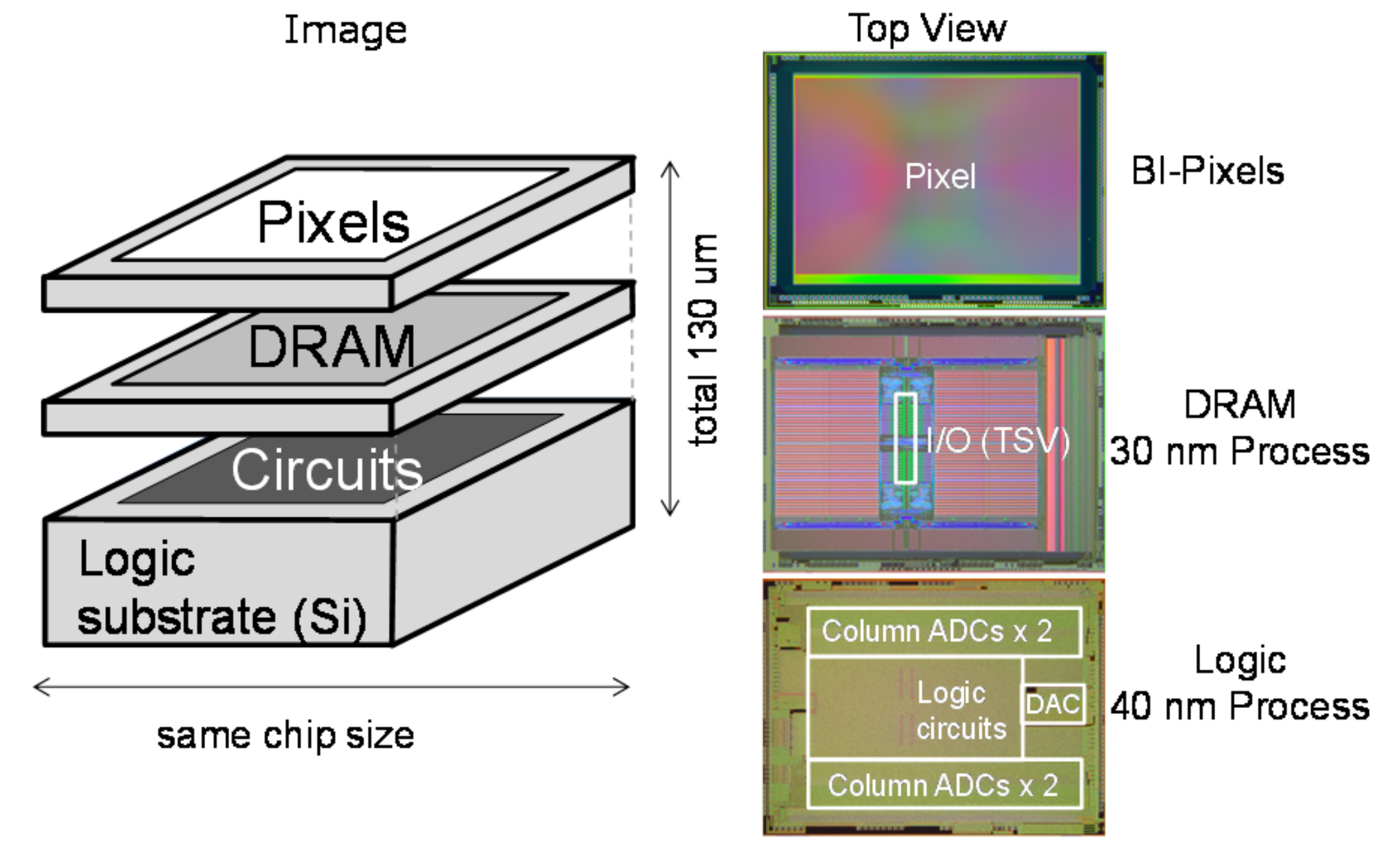

IEDM 2017: Sony’s 3-layer stacked CMOS image sensor technology

At the 2017 IEDM Sony presented their 3-layer stacked state-of-the-art CMOS image sensor (CIS) technology used to minimize rolling shutter distortions and greatly increase the read speed and thus fps through the use of DRAM for temporarily storing the pixel data.

Read more