Arm Launches New Neoverse N1 and E1 Server Cores

Last year, Arm outlined their vision for a trillion connected devices. The vision involves many pieces that must come together. One such component was the Arm Neoverse, the infrastructure side of Arm’s business. The Arm Neoverse covers a diverse set of workloads from the edge to hyperscalers.

Arm’s infrastructure business unit is the company’s fastest-growing business unit and is expected to lead the company in terms of growth over the next five years. They see the boom in infrastructure growth coming from society’s transition from smartphones to an always-connected world of a trillion edge sensors and compute units that will be capable of performing computations at the edge – all generating an order of magnitude more data than today’s smartphones.

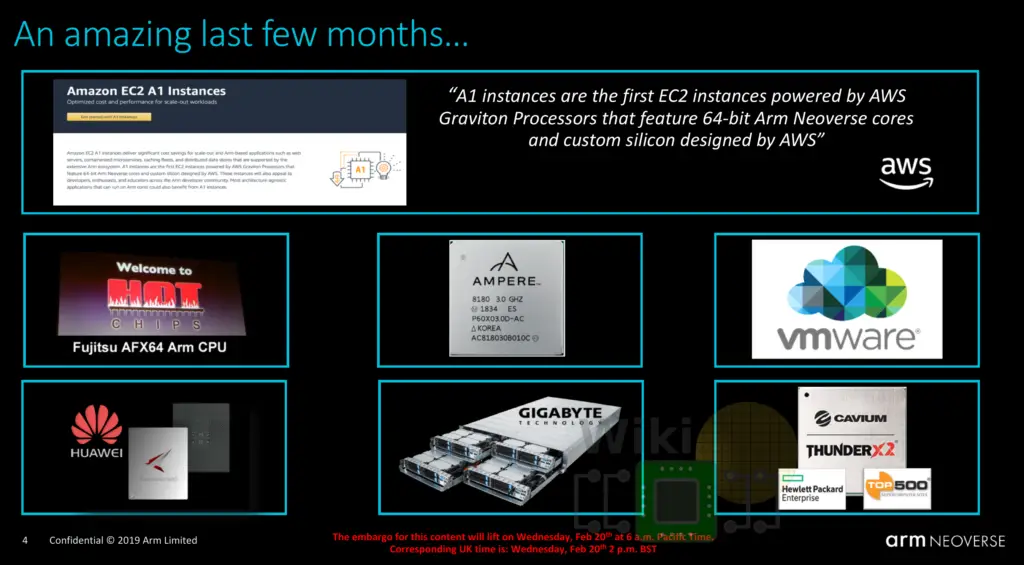

Over the last few months, we have already witnessed some interesting product announcements and rollout and Arm didn’t forget to mention them. Those include Fujitsu’s AFX64, Amazon’s Own AWS Graviton, Ampere’s eMAG, Cavium’s ThunderX2, and Huawei’s Kunpeng 920. It’s worth highlighting that the mixture of products includes company who use Arm’s own IPs to create custom products as well as companies who have developed their own Neoverse cores in order to deliver a unique differentiating product.

In addition to those products, ThunderX2 has also managed to pierce into the TOP500 with the Astra supercomputer, also becoming the first Arm-based system to exceed 1 petaFLOPS.

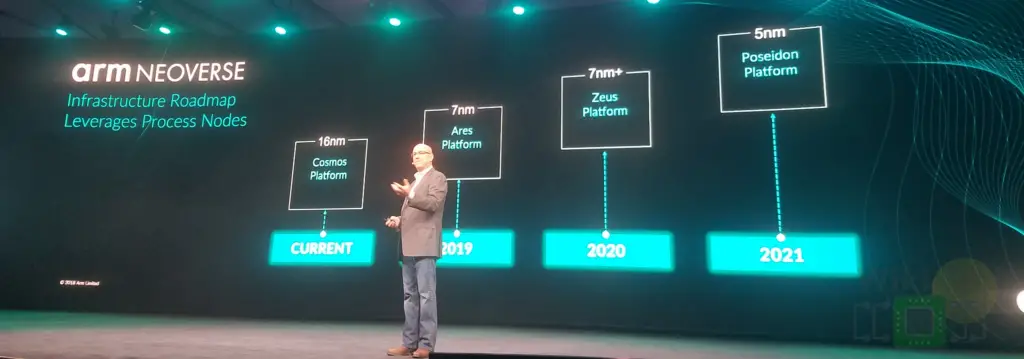

Coupled with those announcements was Arm’s own commitment to an infrastructure-specific roadmap which covers everything from the edge and 5G base stations to storage, security, networking, management, and all the way up to hyperscaler data centers. As part of their announcement, Arm outlined their investment in this segment in the form of a series of new high-performance cores optimized with infrastructure-specific enhancements in mind. Ares, Zeus, and Poseidon are the first three in Arm’s new annual cadence of platforms that will serve as the underlying IP technology for the Neoverse from Arm that companies will be able to use.

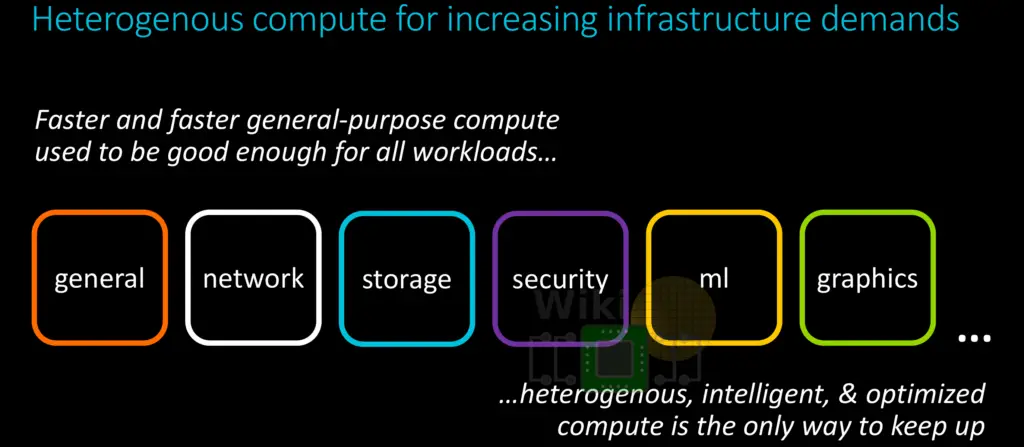

Those cores are not enough and Arm knows that heading into the 2020s the compute landscape will be much more diverse where other types of hardware such as neural processors, GPUs, and other hardware accelerators are required to achieve high performance at high efficiency.

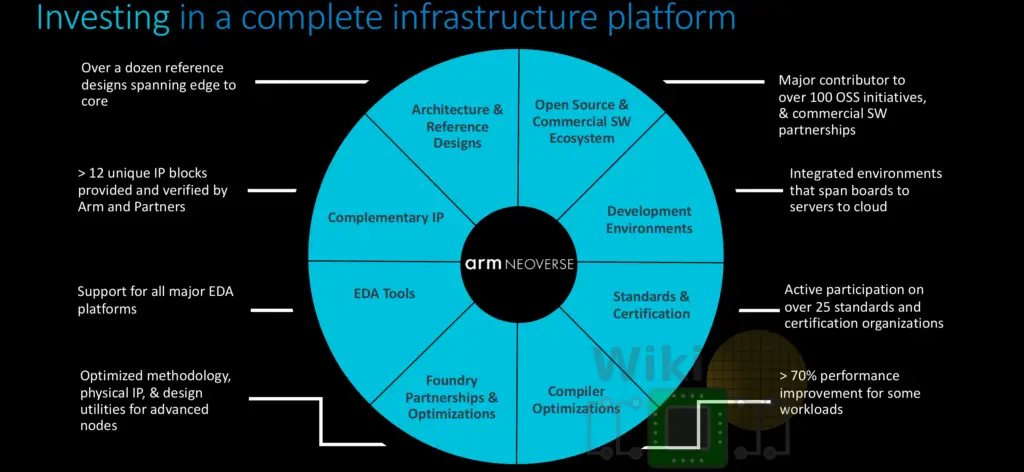

One of the key points that Arm is trying to convey by using the term platforms here is that the CPU on its own still requires an immense amount of work to get to a point where silicon is shipping. To address this, Arm is investing in a complete infrastructure platform to simplify this process as much as possible. In addition to the base CPU IPs, Arm provides the architecture and complete reference designs that allow implements to play with and understand how to use the various IPs Arm offers. Additionally, Arm designs and provides over 12 other unique IP blocks as well as validate other partners IPs to ensure they work within the specifications. It goes without saying that Arm work with all the EDA tools vendors and software partners to make sure IPs work well with their tools. Arm also noted that they work closely with foundry partners (e.g., TSMC) to tune their process so that the final implementation works at a high performance.

Introducing the Arm Neoverse N1 and E1 platforms

Today, Arm is officially introducing the first two Neoverse platforms – the Neoverse N1 and the Neoverse E1.

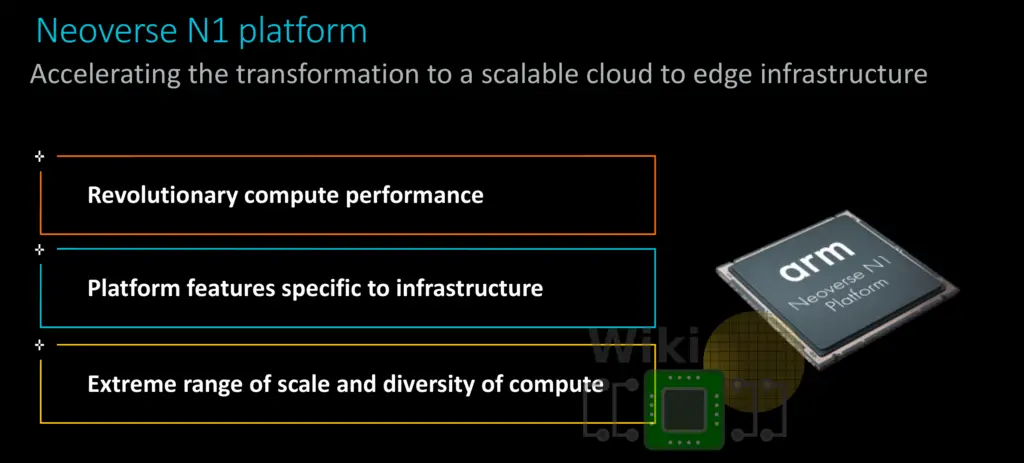

- Neoverse N1 platform – optimized for a leading-edge process, primarily focuses on infrastructure/cloud workload performance

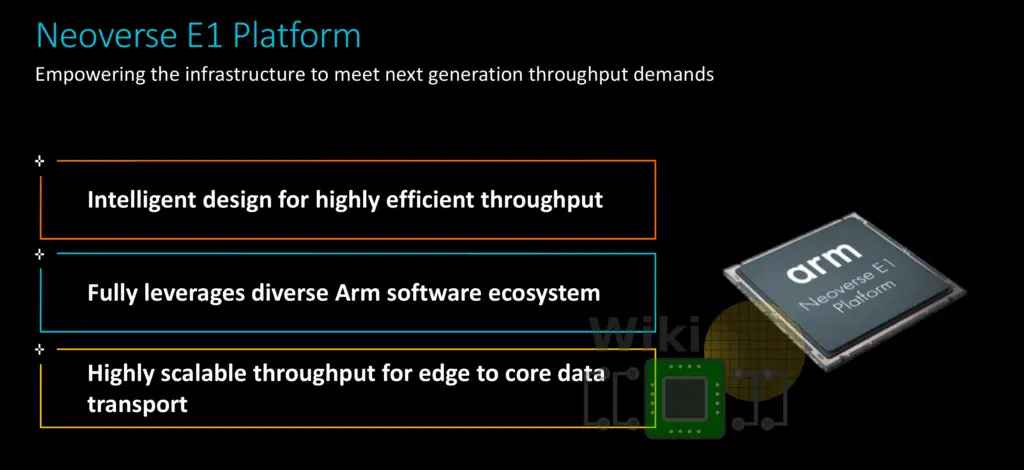

- Neoverse E1 platform – primarily focuses on high-efficiency throughput performance

The Neoverse N1, formerly Ares, targets high-performance compute levels similar to Intel’s own Xeon Scalable levels. The Neoverse E1 platform, on the other hand, was not mentioned back at TechCon last year. The E1 is designed for driving high throughput performance with multithreading support at higher efficiency than that offered by the N1. In other words, Arm is introducing two complementary cores – N1 targeting high compute while the E1 targets high throughput.

|

|

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–