SiFive Launches 7 Series, Their Highest Performance RISC-V Cores

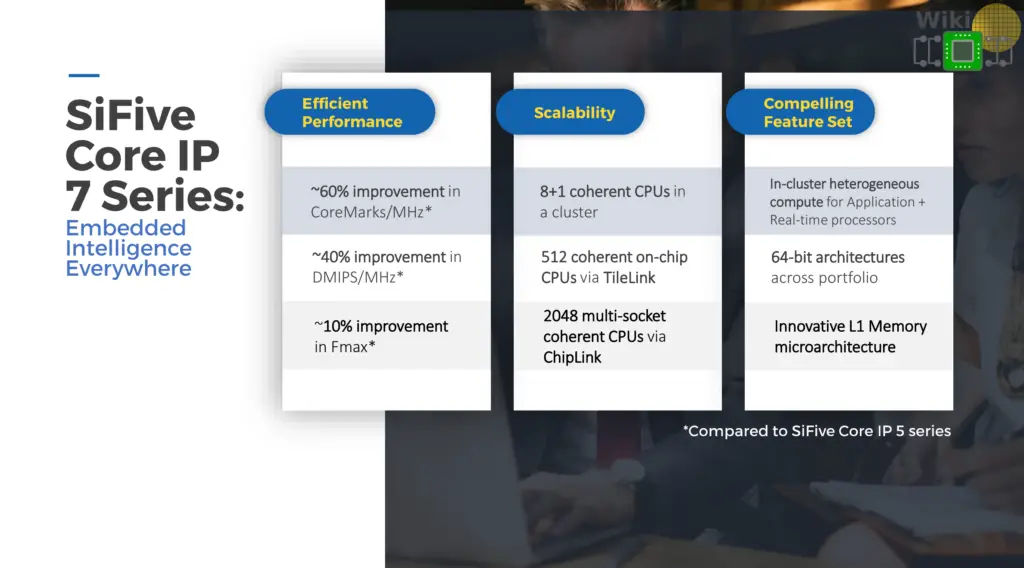

Last week SiFive introduced their 7 Series, the company’s highest-performance RISC-V IP cores. The 7 Series brings significant improvements over the prior 5 Series including what they claim is roughly 60% improvement in CoreMarks/MHz, 40% improvement in DMIPS/MHz, and 10% higher frequency. SiFive says those are the highest performance commercial RISC-V cores on the market.

7 Series

SiFive’s 7 Series is a family of configurable RISC-V cores. They are SiFive newest addition to their Core Designer, a unique a la carte designer that allows customers to further tweak the base design and the microarchitecture to match their needs. Within their 7 Series, SiFive offers three base configurations with known PPAs that customers can start off with.

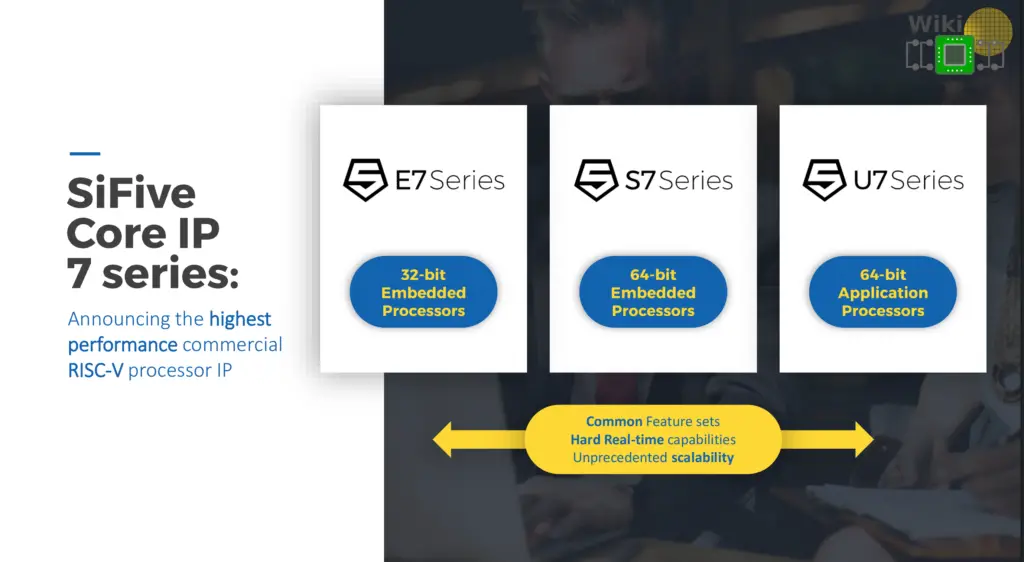

There are three sub-series: E7, S7, and U7. For the most part, those follow SiFive consistent naming scheme. The S7 is a new series that is being introduced with 7 Series which brings 64-bit support for embedded applications. It’s worth noting that all three subseries share the same base architecture and most of the feature set.

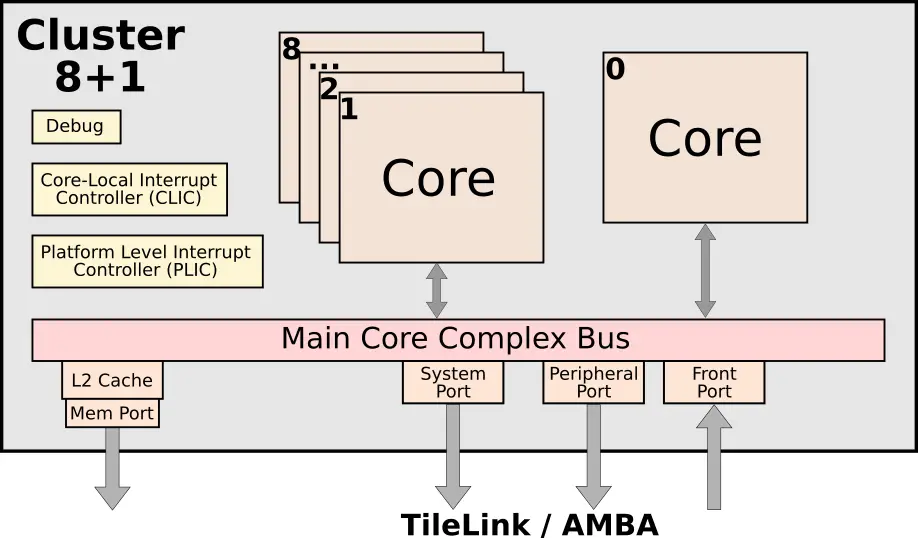

The basic 7 Series block is a complete cluster which can incorporate up to 9 (8+1) cores. The combination of cores, as well as the type of memory, can be configured. For example, a single cluster can incorporate a number of S7 cores along with U7 cores and those cores can have tightly integrated memory (TIM) or standard caches with ECC. SiFive also allows for custom instructions through the use of RISC-V custom extension abilities. By the way, those clusters need not incorporate just 7 Series cores. SiFive supports mixing 7 Series with other cores such as their high-efficiency 2 Series cores.

This design scales further with up to roughly 64 of those clusters can be integrated on a single chip via TileLink.

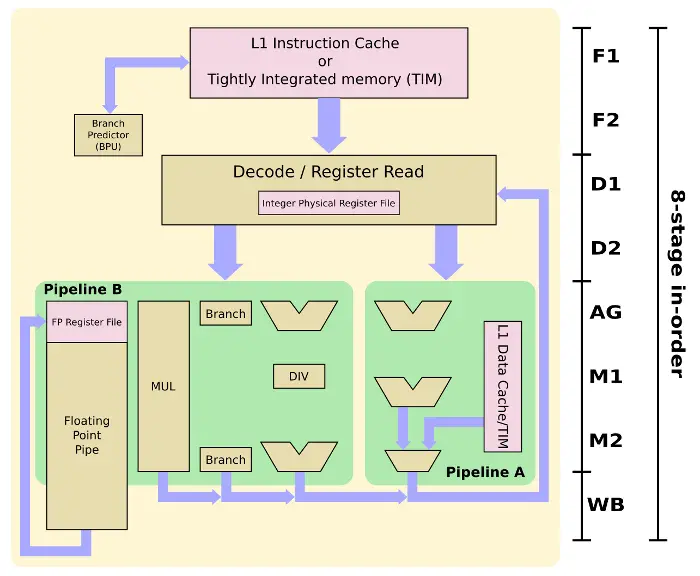

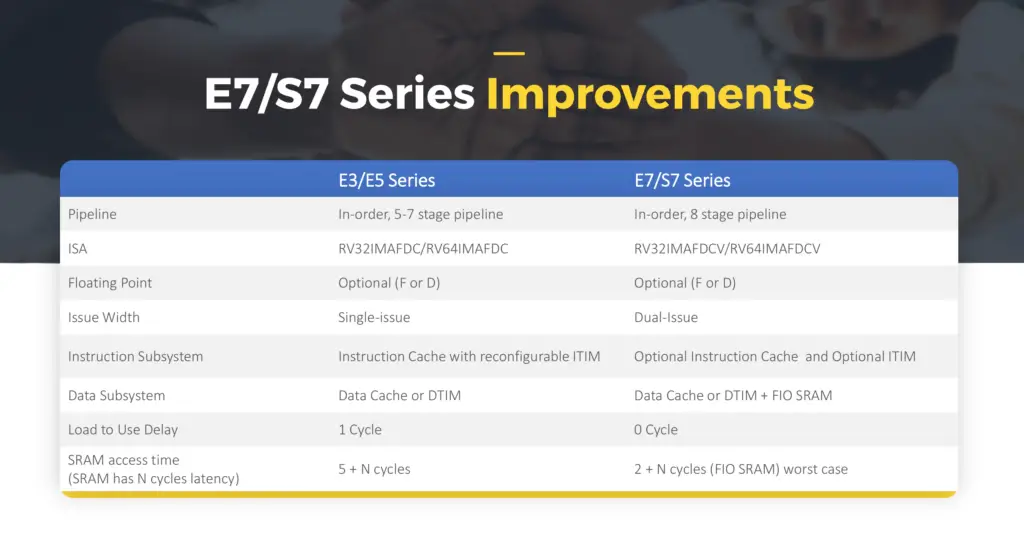

Within the 7 Series, all the cores are based on the same underlying microarchitecture. 7 Series is based on a new 8-stage pipeline. Prior series (i.e., E3/E5) were based on a 5-7 stage design. The new pipeline is now wider too. This is a dual-issue in-order design.

SiFive improved the memory subsystem a fair bit. One improvement that was made is 0-cycle load-to-use latency. This is done through the use of two ALUs for both pipes (at the address generation stage and at the M2 stage), enabling an ALU operation after a data load operations. There is also optional configurable cache and instruction TIM as well as optional data TIM.

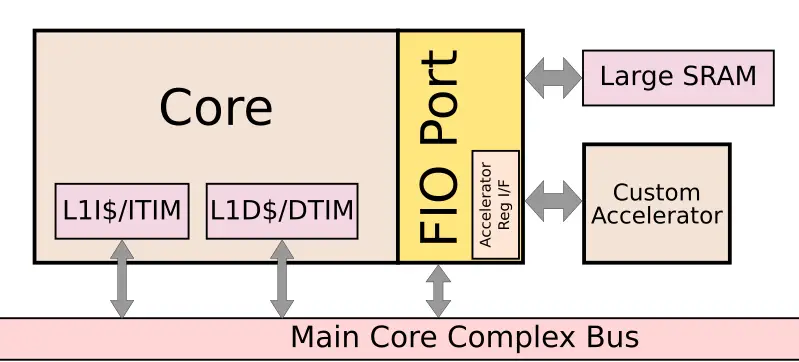

SiFive also added what they call the fast I/O port (FIO Port). The FIO port is optional and is attached directly to the core and is designed to serve as a low-latency interface directly between the core and a large attached SRAM or an accelerator.

One thing to note is that the FIO port also interfaces with main core cluster bus, allowing other cores to see those accelerators or additional memory in a coherent way.

SiFive says lead customers already have RTL for the 7 Series and are working on tapeouts for 2019.

What’s Next?

It’s often said that the product release cycle can be used as a proxy for motoring the health of a company. SiFive is operating on a very aggressive design cycle.

| 2018 Product Release | |

|---|---|

| Date | Product |

| Feb. 7, 2018 | Freedom U540 SoC |

| June 25, 2018 | E2 Series |

| October 31, 2018 | 7 Series |

It’s hard to quantify their success just yet but we do know they have scored a number of design wins this year including FADU’s SSD controllers that will use SiFive E51 multicore IP cores and Huami who is designing wearables powered by RISC-V. Earlier this year SiFive secured a $50.6 million Series C funding, bringing the total investment in SiFive to $64.1 million. WikiChip expects SiFive aggressive development cycle to continue with more powerful, likely out-of-order, cores in the future.

Derived WikiChip articles: 7 Series.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–