Ampere Ships First Gen ARM Server Processors

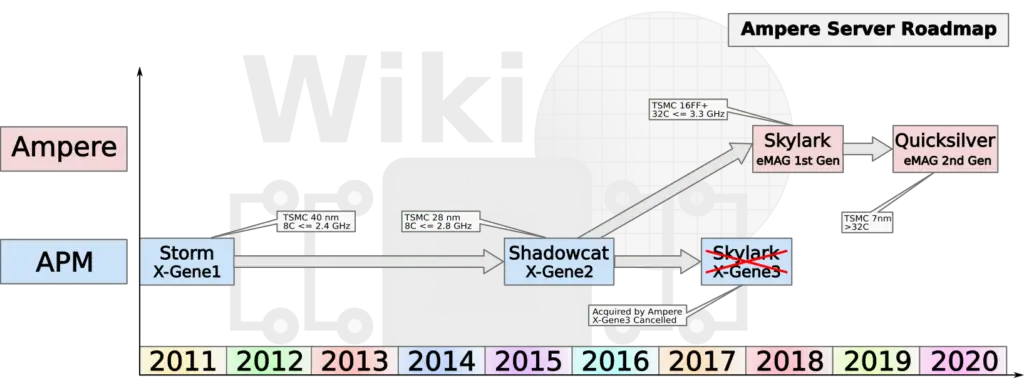

Ampere Computing has announced that they have begun shipping their first-generation product – eMAG. Picking up where AppliedMicro left off, fabicated on TSMC’s 16nm process, the eMAG family are multi-core ARMv8-A processors for the data center. Next to Cavium’s ThunderX2, Ampere is now the second chip company shipping high-performance ARM server processors for the data center, albeit their market is slightly more limited to single-socket solutions.

Ampere Computing has announced that they have begun shipping their first-generation product – eMAG. Picking up where AppliedMicro left off, fabicated on TSMC’s 16nm process, the eMAG family are multi-core ARMv8-A processors for the data center. Next to Cavium’s ThunderX2, Ampere is now the second chip company shipping high-performance ARM server processors for the data center, albeit their market is slightly more limited to single-socket solutions.

eMAG

Ampere announced the availability of two eMAG processors.

| Ampere eMAG | |||

|---|---|---|---|

| Processor | 8180 | ? | |

| Price | $850 | $550 | |

| Cores | 32 cores | 16 cores | |

| Frequency | 3.3 GHz Turbo | ? | |

| Memory | 8 × DDR4 Chans | 8 × DDR4 Chans | |

| PCIe | 42 Lanes | 42 Lanes | |

| TDP | 125 W | ? | |

At $850, the 32-core model comes at exactly one hundred dollars less than their initial estimated price tag. Ampere did not disclose much info about the 16-core beyond the price but we don’t expect it to differ much from the 32-core variant. Ampere’s top binned chip is the eMAG 8180. And yes, it does sound eerily similar to Intel’s current top binned chip, the Platinum 8180. This processor features 32 ARMv8.0-A cores operating at 3 GHz with up to a 3.3 GHz turbo along with eight DDR4 memory channels. Since we don’t know much about the performance of those cores, it’s hard to pinpoint the most comparable x86 equivalent.

Skylark

The new eMAG processors are based on the 16 nm Skylark microarchitecture, a design that started by AppliedMicro which has eventually found its way to Ampere along with most of the design team. In fact, first-generation Ampere eMAG processors are what was planned to become X-Gene 3. Next year, Ampere plans to follow up on this architecture with their next-generation servers, Quicksilver, which will be on TSMC 7nm.

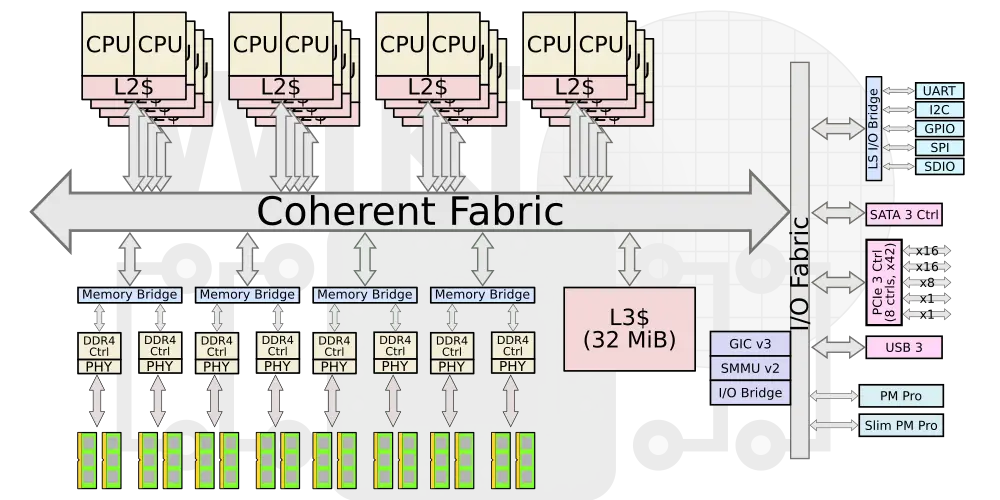

The chip is fully compliant with the Arm server SBBR and SBSA standards (level 3 so there is EL3 and CRC32 support). The architecture comprises 16 core duplexes called processor modules. Each module has two custom-designed ARMv8.0-A CPUs along with 256 KiB of shared L2 cache. Each core is a 4-way out of order superscalar that has a 32 KiB private L1 instruction cache and a 32 KiB private L1 write-through data cache. At this high level the architecture is identical to Shadowcat, however, Ampere had mentioned that various microarchitectural enhancements were made so presumably, the OoO backend grew. Compared to the previous generation, the target frequency was increased to 3 GHz with a 3.3 GHz turbo.

The processor module is cloned 16 times to form the full chip. Scaling up the core count is not straightforward and was something they paid close attention to. The processor modules are hooked onto a coherent fabric which was revamped to support a large number of cores (beyond 32). Attached to the fabric is the large 32 MiB shared L3 cache and double the memory controllers. Skylark doubled the memory channels to 8 for a total of 16 ECC DIMMs and 1 TiB of memory.

Ampere is financed by the Carlyle Group and we are hearing they are very well-funded, enough to keep development going for a while. They have partnered up with Lenovo as their lead partner for building the platform around the eMAG brand. Looking forward to 2019, Ampere is expected to further future-proof their SoC with PCIe Gen 4 support and CCIX connectivity. Quicksilver will also bring multi-socket support which would put them on an equal footing with Cavium’s ThunderX2 among other changes such as higher core count and higher IPC.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–