Intel Unveils the Tremont Microarchitecture: Going After ST Performance

Additional Features

Tremont will be integrated into additional products such as Snow Ridge 5G edge computing chip, there are some new accelerator-interfacing instructions. Those are essentially ways to write data to things like networking and processing engines in a weak and fast manner. You can think of them as instruction-level WCBs but there are a few subtle differences. The first is that data is guaranteed to be delivered and will never be overwritten prior to being sent. And secondly, data is sent immediately to the target device instead of getting queued up and send in bursts.

Tremont also introduces a number of new technologies that were previously only found in the big cores. There is new support for boot guard and TXT. There is also new support for Speed Shift Technology which adds autonomous P-states, allowing the hardware to control the frequency changes, allowing for faster response. Tremont also adds Total Memory Encryption.

>1.3x IPC Uplift

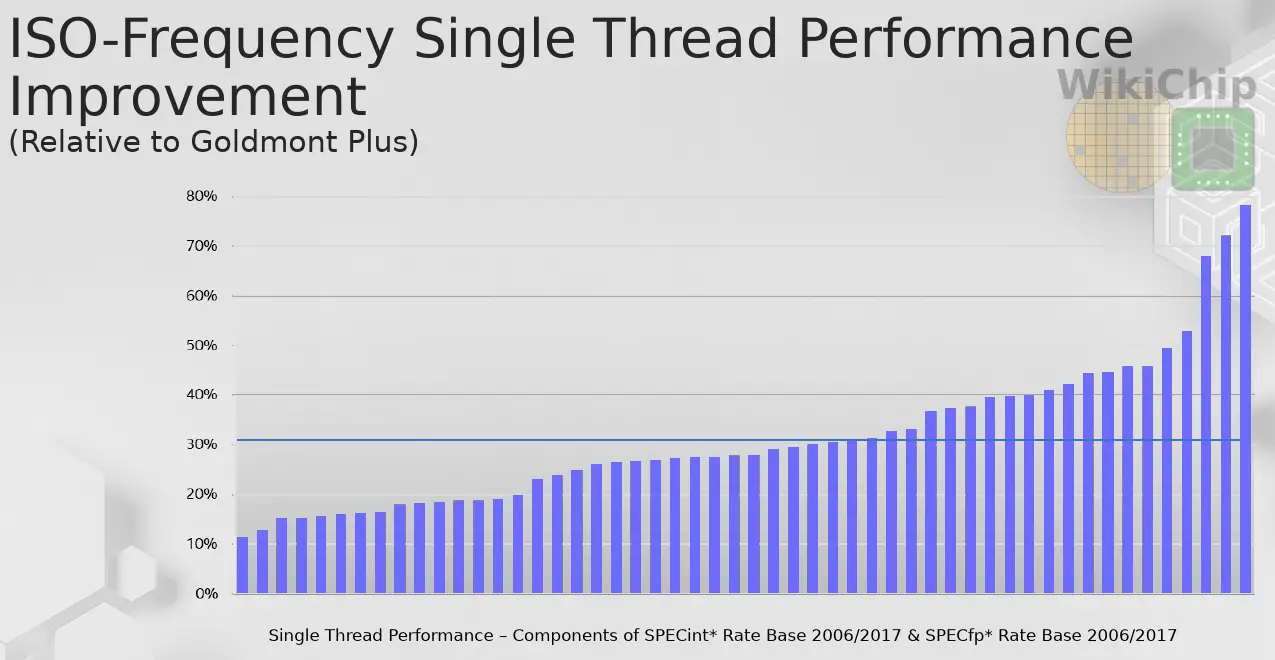

The improvements to Tremont are pretty significant. Intel is reporting over 30% IPC uplift on common industry benchmarks versus Goldmont Plus at ISO-frequency. Though they are not disclosing die size and such at this time, they expect Tremont to be more performance efficient than Goldmont Plus. Currently, Intel is not disclosing the frequency range Tremont covers. By the way, it’s worth adding that Goldmont Plus already has pretty sizable IPC improvement over Goldmont. Considering Intel’s last Atom-based server processors, codenamed Denverton, are based on Goldmont, if the next generation is based on Tremont the performance uplift should be very significant.

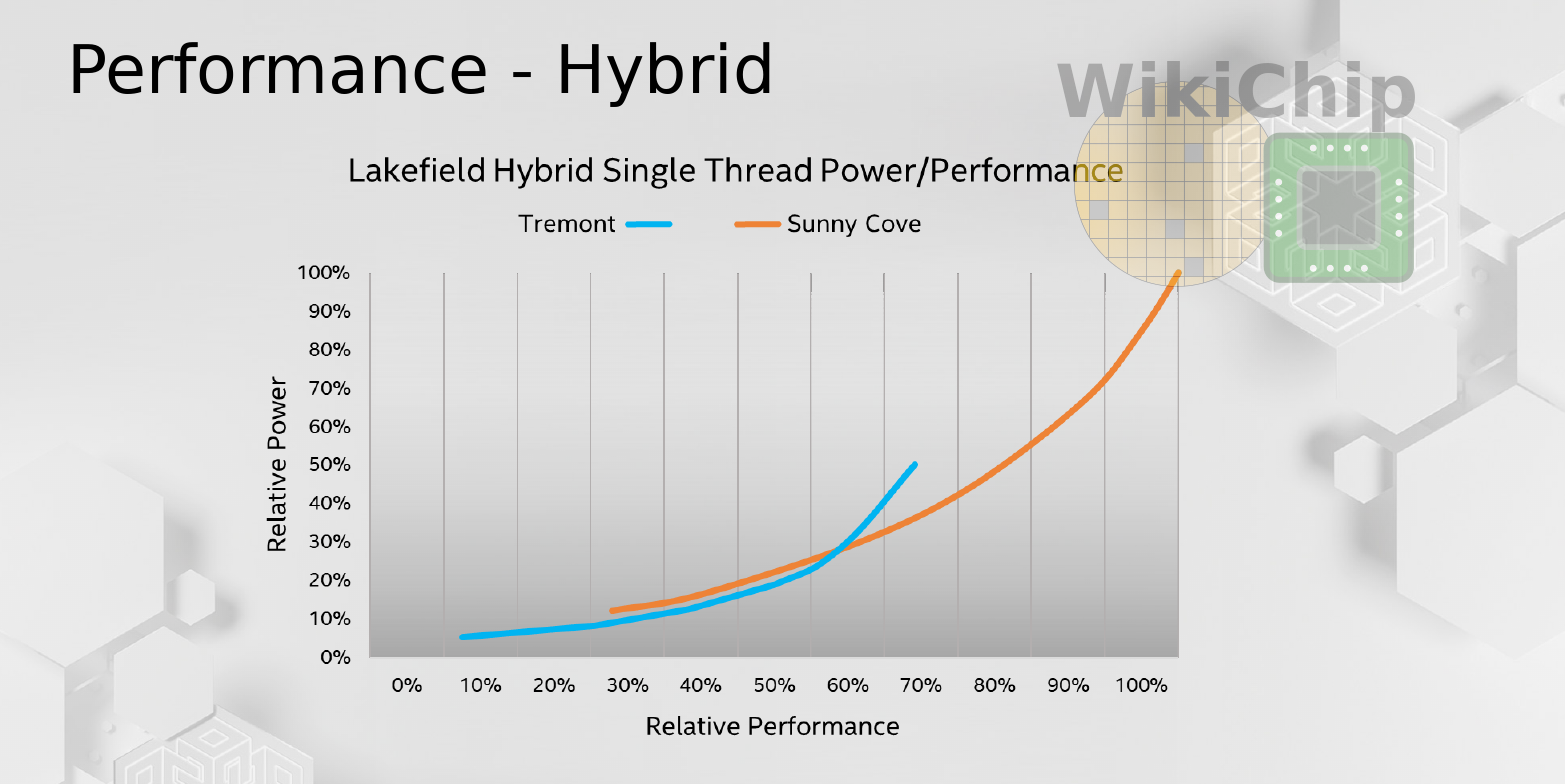

We cropped down the picture to just the graph but note that the footnote for asterisk in the slide just says “Based on performance projections as of October 2019 and subject to change, with SOCs at ISO frequencies.” Since the first product to integrate Tremont is Lakefield, it’s worth comparing the performance and power of Tremont versus Sunny Cove. The graph below by Intel gives a good sense of where those cores are positioned. Though they can reach much lower power levels, Tremont is able to do pretty well compared to Sunny Cove – past the 70% relative performance mark, albeit at a loss of efficiency, Tremont is somewhere between the Sandy Bridge and Haswell level of performance. Given Intel’s next few generations of small cores target high single-thread performance improvements, it won’t be too long before it reaches the levels of today’s Skylake (assuming ~3 GHz range).

One last thing worth pointing out is that Lakefield incorporates a big Sunny Cove core which comes with AVX-512 along with four Tremont cores that have no AVX at all. For products that come with mixed cores, the nominal instruction set is only SSE without AVX. In other words, there is no ISA incompatibility and there is currently no asymmetric ISA support.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–