IEDM 2017: AMD’s grand vision for the future of HPC

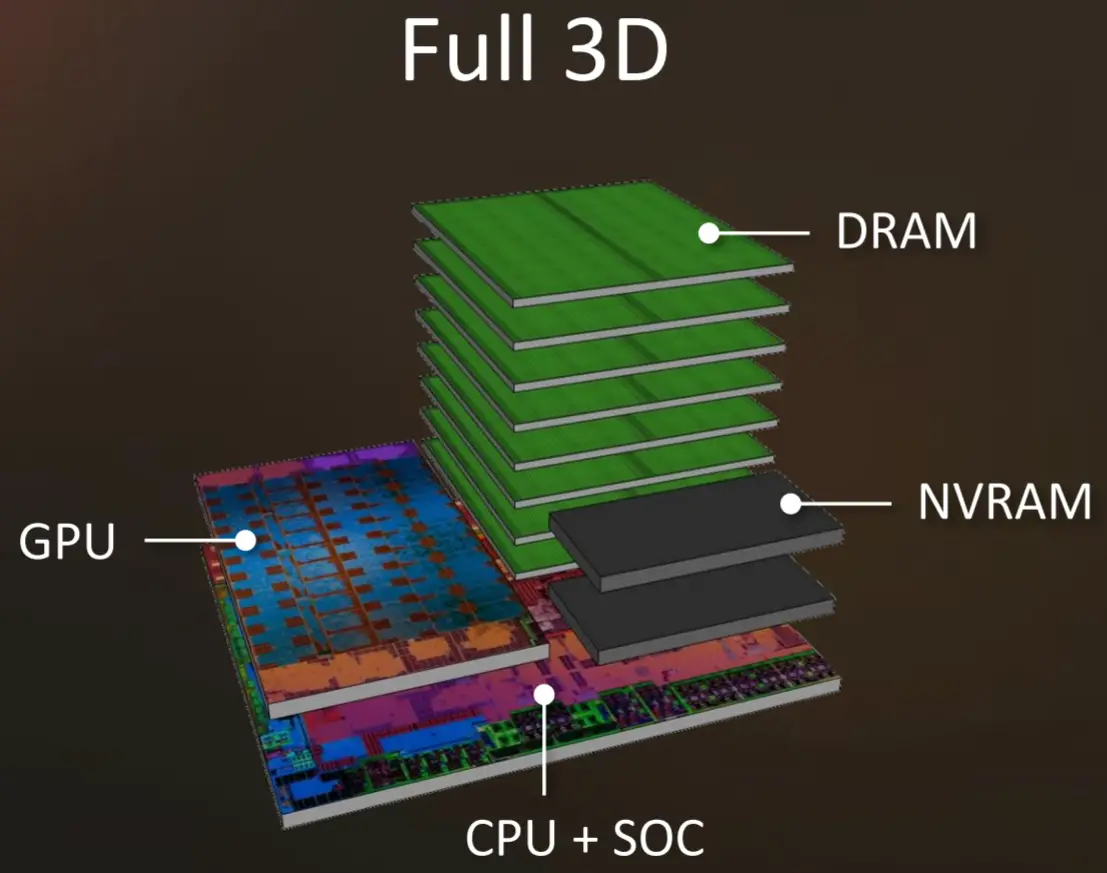

Capping off a great year, AMD CEO Lisa Su opening address at IEDM 2017 highlighted key challenges for the future, predicting a paradigm shift in the design of processors and systems that will deliver another decade of performance gains.

Read more