Intel Looks to Advanced 3D Packaging For More-than-Moore to Supplement 10- and 7-Nanometer Nodes

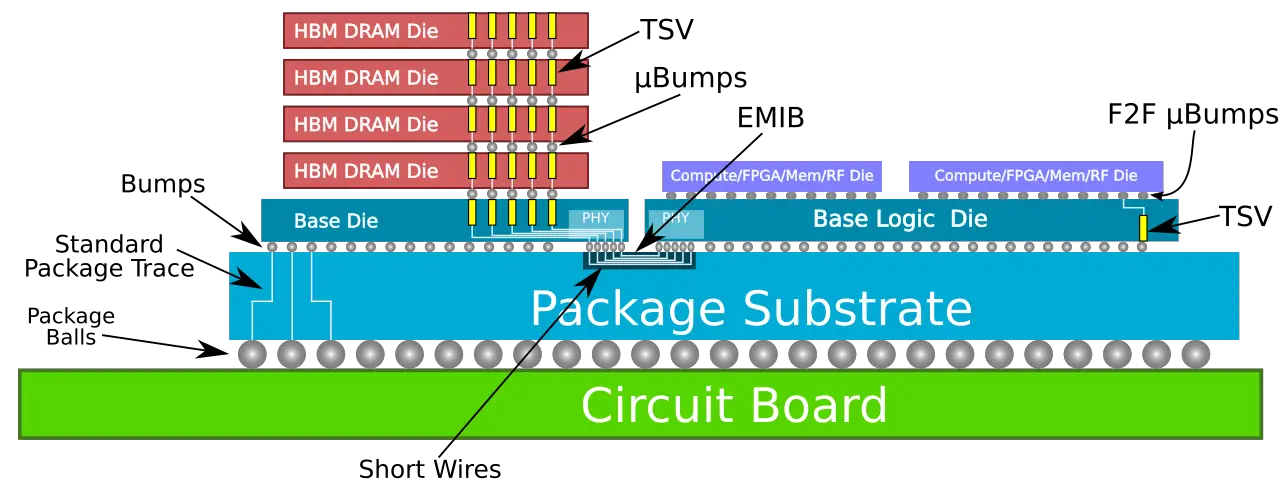

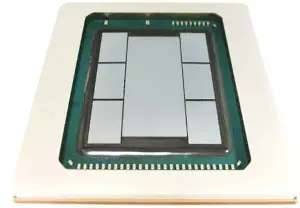

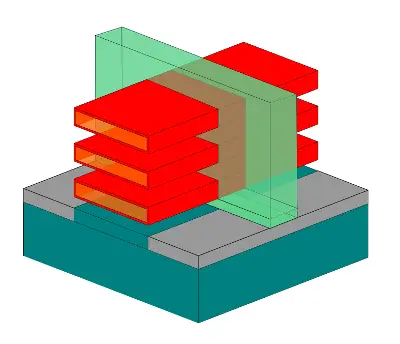

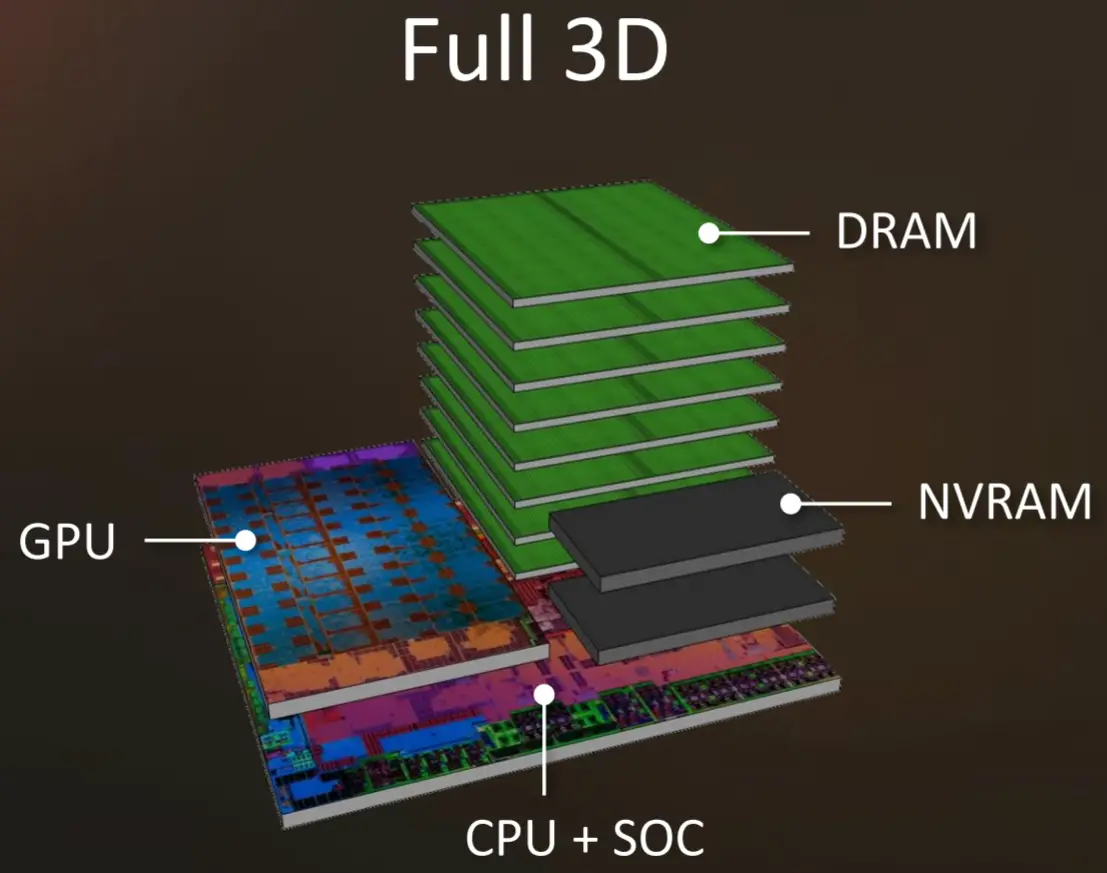

At the recent Intel Architecture Day, the company unveiled their latest advanced packaging technology called Foveros, a face-to-face three-dimensional (3D) die stacking packaging technology in an effort to assist with the slowing of Moore’s Law.

Read more