TSMC Q4: 7nm Dominates Revenue, Preps 5nm Ramp, 6nm By EOY

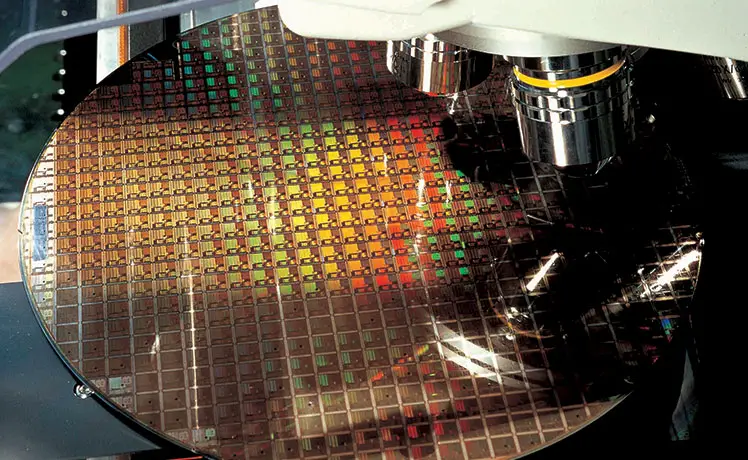

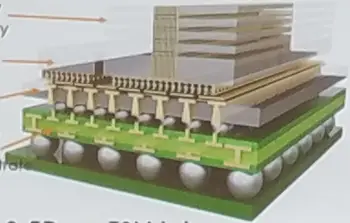

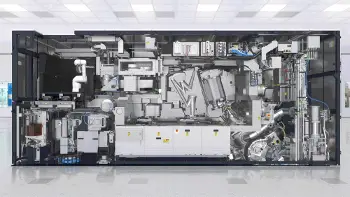

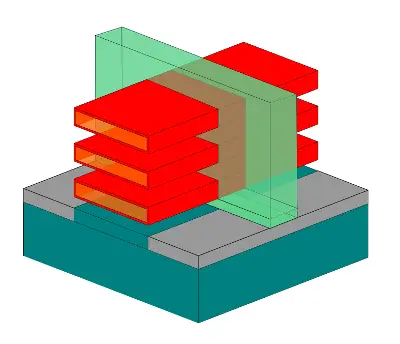

7-nanometer contributes the lion’s share of wafer revenue to TSMC’s fourth-quarter driven by growth from smartphones and HPC. The foundry is also preparing the 5-nanometer node for early this year and the 6-nanometer by the end of the year.

Read more