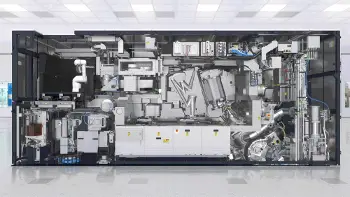

ASML Q4: NXE:3400C Machines Ramp; Strong Growth Due to EUV in 2020

ASML saw a strong fourth-quarter in 2019 thanks to a large EUV shipment with the production of NXE:3400C machines ramping up. ASML shipped a total of 26 EUV machines in 2019 and with 35 machines expected for 2020, however, backlog continues to grow.

Read more