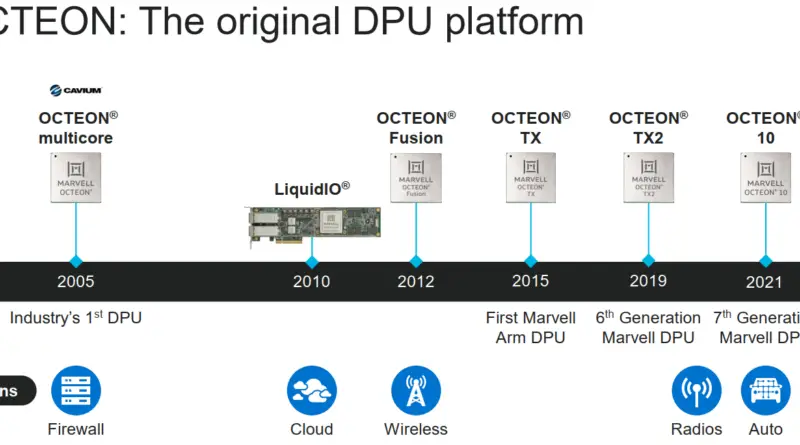

Marvell Launches 5nm Octeon 10 DPUs with Neoverse N2 cores, AI Acceleration

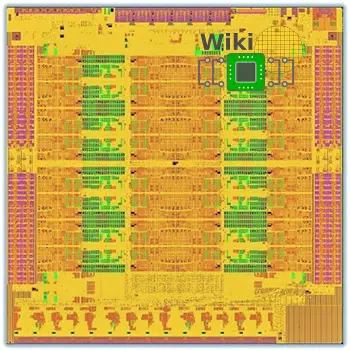

Marvell launches the OCTEON 10 DPU series. Fabricated on a 5 nm process, these chips integrate Neoverse N2 cores, AI acceleration, vector packet processing acceleration, a 1 terabit switch, and the latest DDR5 and PCIe 5.0 I/O interfaces

Read more