Fujitsu Completes Post-K ARM CPU Prototype

Earlier this week Fujitsu announced that they have completed the Post-K prototype CPU. The new domestically-designed microprocessor has commenced functionality field trials. The prototype will be exhibited next week at the 2018 International Supercomputing Conference (ISC) in Frankfurt, Germany.

Post-K Computer

The Post-K CPU is a joint collaboration between Fujitsu and RIKEN. The processor is expected to power the Post-K Computer at RIKEN which should commence operation around 2021 (same timeframe as Aurora and Frontier). The system is unique in a number of ways. Whereas prior supercomputers developed by Fujitsu used SPARC64, Post-K is their first ARM-based system. Fujitsu and RIKEN are also working on a custom ARM compiler for the system. While the compute power has yet to be disclosed, the goal of Post-K is to deliver 50-100x the application performance of the K Computer.

Fujitsu released some initial specs for the machine.

| Post-K Computer | |

|---|---|

| Node | 1 CPU/Node |

| Rack | 384 Nodes/Rack |

| Interconnect | Tofu3 |

| File System | Fujitsu Exabyte File System (FEFS, Lustre-based) |

| System Power | 30-40 MW |

| Performance | 50-100x Real application performance of K Computer |

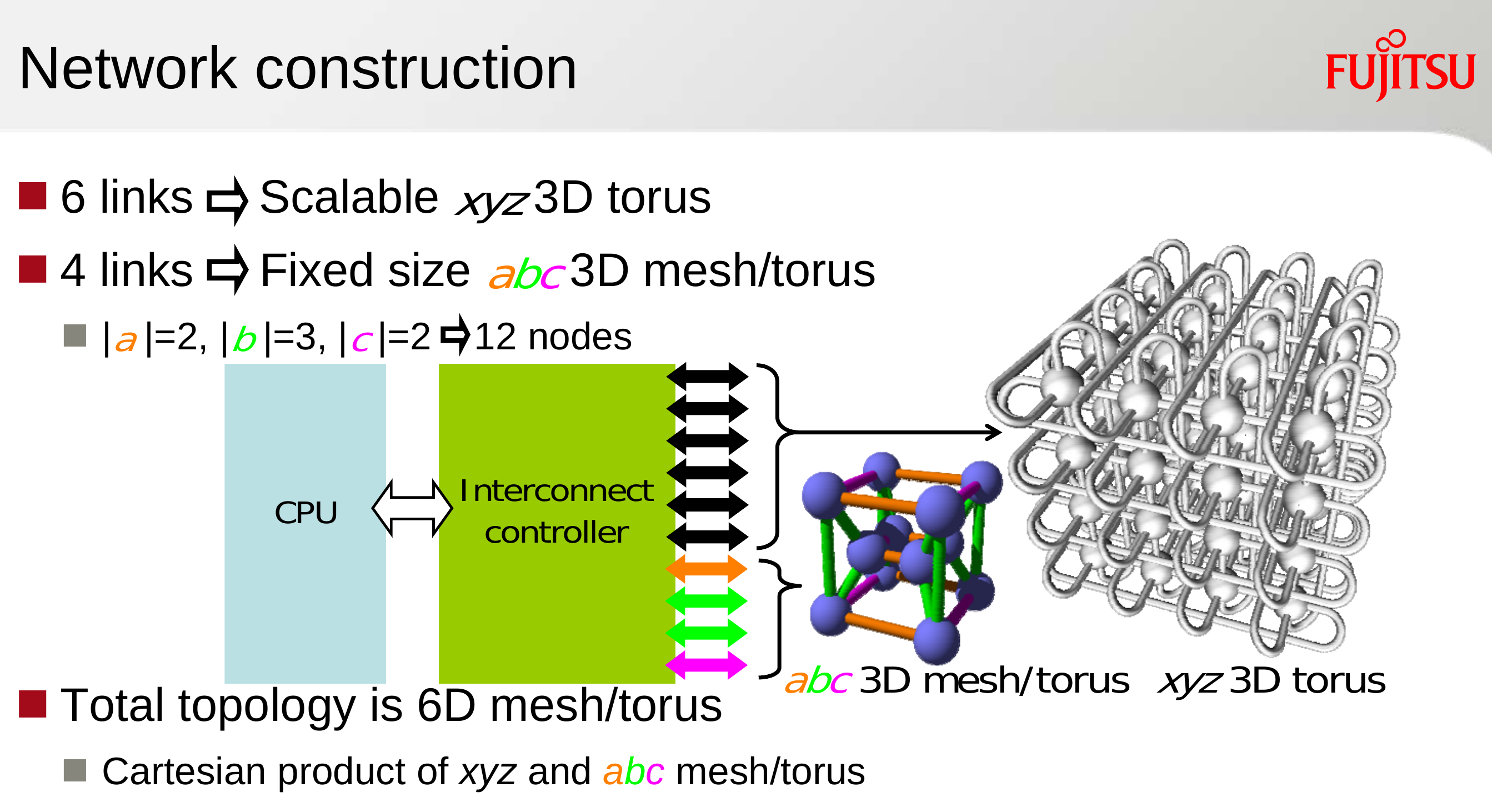

The number of racks in the system is currently unknown and while they are aiming for 50-100x real application performance of the K Computer, RIKEN has yet to commit to any hard performance numbers. As far as storage is concerned, the system also features a 3-level storage hierarchy system. Post-K utilizes the Tofu3 6D mesh/torus interconnect architecture which is a third-generation enhanced version of the original interconnects found in the K Computer.

Post-K CPU

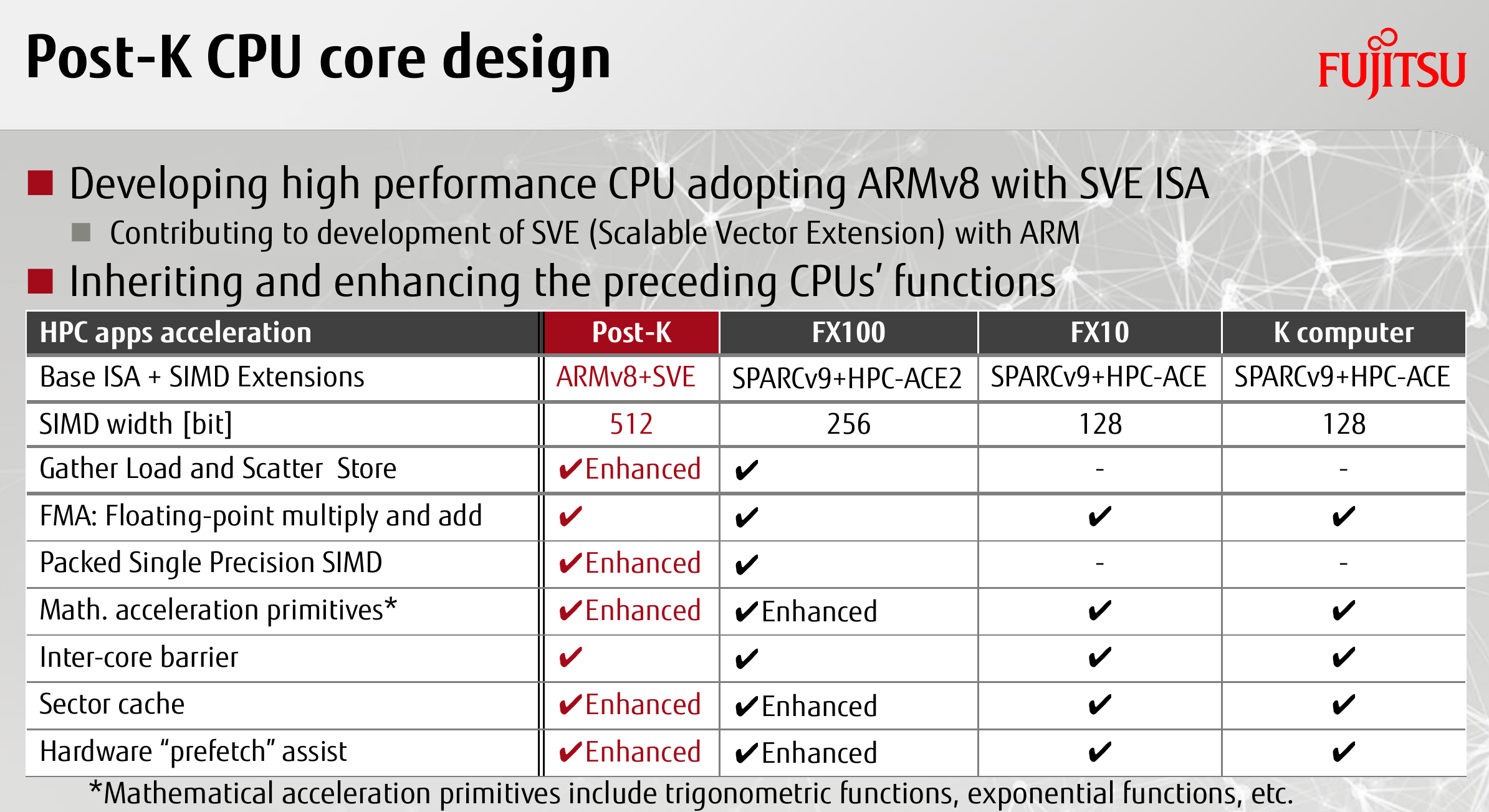

The new microprocessor is based on a custom designed Fujitsu many-core microarchitecture that implements the ARMv8-A ISA. Each microprocessor has 48 cores plus 2 assistant cores (or 4 assistant cores in the case of I/O nodes). Each core also supports the ARM Scalable Vector Extention (SVE) with 512-bit wide SIMD operations as well as a number of custom Fujitsu extensions.

| Post-K CPU | |

|---|---|

| Node | 1 CPU/Node |

| ISA | ARMv8-A |

| SVE | 512-bit |

| Memory | 3D stacked DRAM (HBM 3/4?) Terabyte/s BW |

| Cores/Chip | 48 compute cores + 2 assistant cores (Compute nodes) 48 cores + 4 assistant cores (I/O + Compute nodes) |

| Cores/Rack | 18,432 compute cores / Rack |

Although the memory specifications have not been disclosed, we were told it’s on the order of Terabyte/s bandwidth using 3D stacked DRAM. We will know more about the processor in August when Toshio Yoshida from Fujitsu will be presenting the processor at Hot Chips 30.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–