IEDM 2017: GlobalFoundries 7nm process; Cobalt, EUV

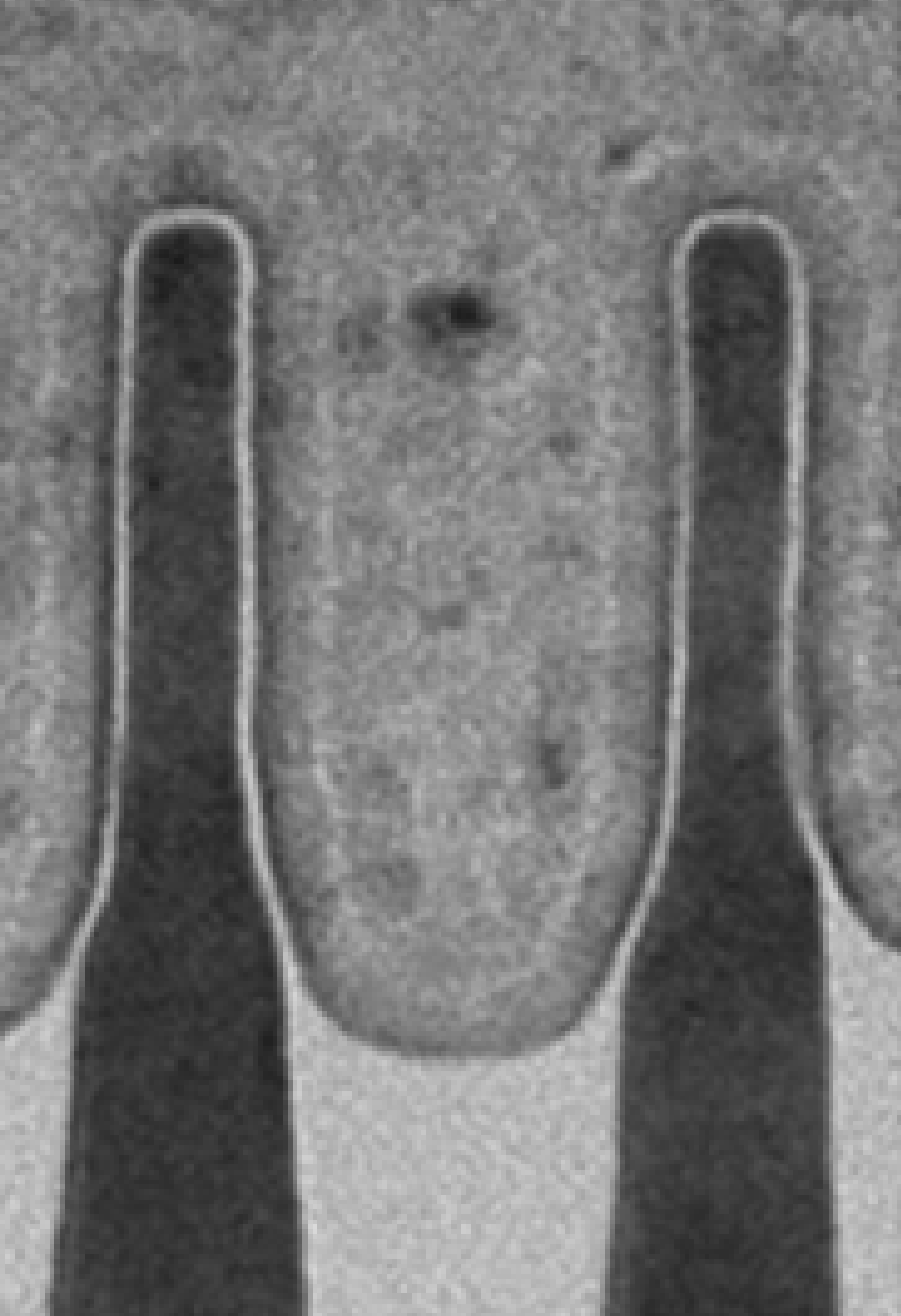

At the 2017 IEDM GlobalFoundries detailed their 7nm Leading Performance (7LP) process, an aggressively scaled version of their 14nm process optimized for next-generation mobile, SoC, and high-performance applications.

Read more