Hot Chips 30: AMD Raven Ridge

Power Delivery

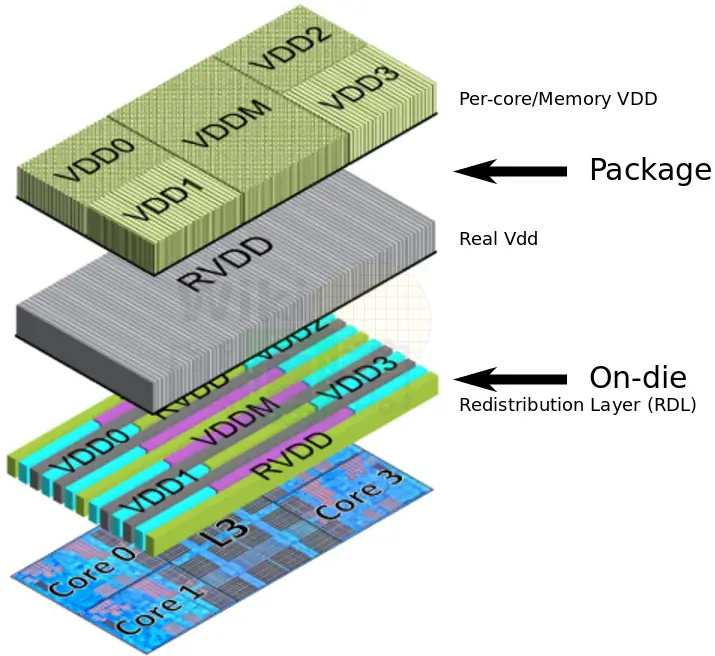

Back in Bristol Ridge, there were three independent primary rails coming into the chip – SoC, Graphics, and CPU. That configuration meant that both the CPU and Graphics rails were overprovisioned for worst-case (i.e., maximum power to account for possible GPU/CPU overlaps). This means that for all other power states, you are operating less efficiently than it could be. In Raven Ridge, the two voltage rails have been combined into a single rail (i.e., a single Vdd). Like in the design of the Zeppelin, the real VDD (RVDD) is fed from the VRM into the chip which is distributed in the package to the individual cores. Since Raven Ridge includes the Vega graphics, the real VDD is extended to the graphics engine. Each of the Zen cores and Vega compute units has its own local low drop-out regulator that takes the RVDD as input, forming its own voltage domains. Back at ISSCC, AMD disclosed that at the package-level, the RVDD is controlled by a platform voltage regulator with a granularity of 6.125 mV whereas the LDOs supply the individual cores with a much finer granularity of 2 to 3 mV per step. Raven Ridge should be fairly similar to those values.

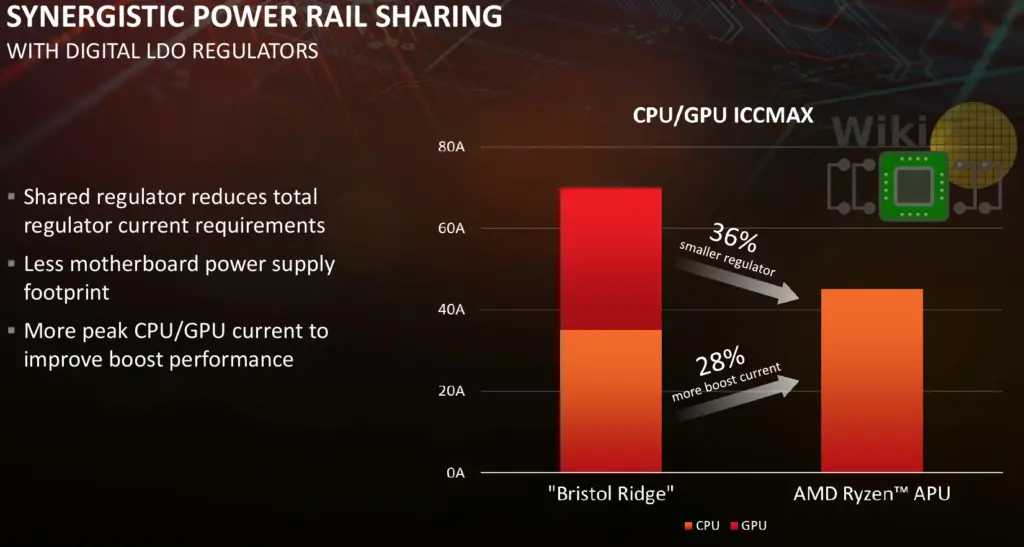

By the way, since AMD eliminated the second voltage rail, less pins were required for the package which is one of the key enablers that allowed AMD to use a smaller BGA package. Note that this is relevant only to mobile parts as desktop Raven Ridge chips use the standard AM4 socket. AMD reports that the single voltage rail which requires 36% smaller area for the regulator provides them with a 28% increase in current. In other words, by sharing the same rail, the total package-level current required has been reduced while the peak current allowed for either the GPU or CPU was increased.

Granular OFF States

The use of distributed LDOs meant they can have more granular control over the power states of the chip. The Raven Ridge power management state control was enhanced to take advantage of the new localized power domains. For the quad-core CCX, with each core fed from its own power regulator, each core can be independently powered down (CC6). Entering PC6 (CPUOFF) means the caches power can also be lowered. On the GPU side, very fast (< 100us latency) shut-offs are possible along with complete power gating of the graphics (up to 95% of the power) is also possible.

STAPM

Raven Ridge features an improved version of the Skin Temperature Aware Power Management (STAPM) which was introduced in prior generation of APUs. Under STAPM, the cores can be temporarily boosted in order to exploit the temperature excursion of the device. In other words, the delta between the Tskin and Tambient can be exploited in order to provide a short bursts of additional performance while the device is relatively cool without exceeding the skin temperature. This technique mainly improves user experience and sparse bursty workloads similar in behavior to many other power management mechanisms including Intel’s TVB.

25×20

Bouvier did not forget to reflect on their progress toward the 25×20 Energy Efficiency Initiative. The goal, which started back in 2014, is to reach 25x power efficiency by the year 2020. This is achieved through process technology advancement, compute performance, power delivery, power management, and idle power optimizations. To that end, AMD claimed to have been making significant progress. By the way, the slide presented at Hot Chips lists Raven Ridge for both 2017 and 2018. Moreover, the graph appears to show a bigger jump from 2017 to 2018 than the jump from Bristol Ridge to Raven Ridge. It’s unclear what the ‘2018 Raven Ridge’ refers to but the slide footnote does say “Data source: AMD confidential based on internal test results of upcoming ‘Raven Ridge’ APU”.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–