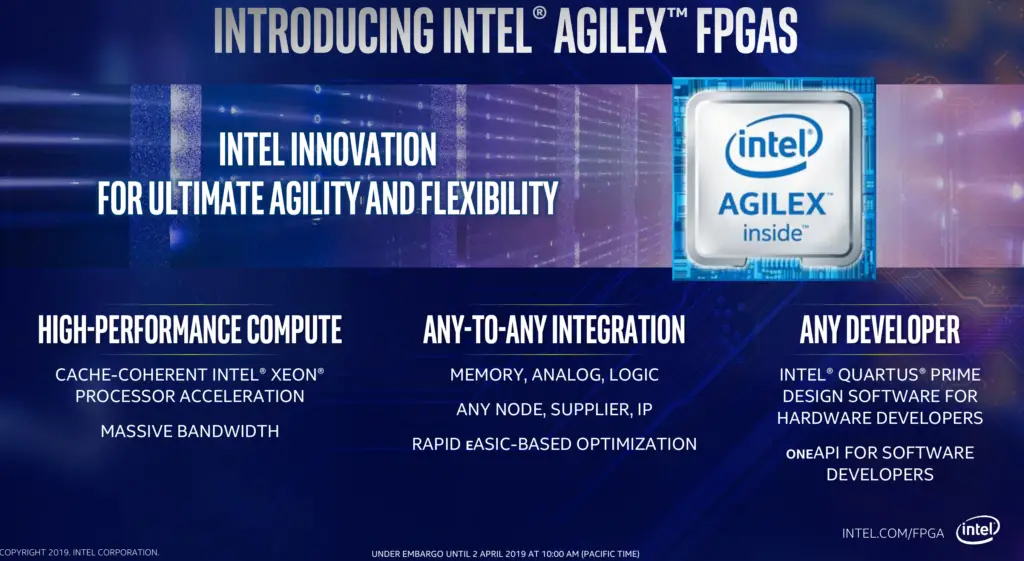

Intel Introduces 10nm Agilex FPGAs; Customized Connectivity with HBM, DDR5, PCIe Gen 5, and 112G Transceivers

As Intel slowly recovers from its 10-nanometer woes, we are finally seeing some concrete announcements. As part of today’s Intel Data Center event, the company is pulling the curtain back on its data-center oriented line of high-performance FPGAs.

Introducing Agilex

Today, Intel is introducing Agilex FPGAs, formerly codename Falcon Mesa. Those FPGAs are based on Intel’s 10-nanometer node. Intended to serve as the company’s next-generation flagship line of FPGAs, those chips are aimed at accelerating data center workloads, network and storage, 5G applications, and other edge applications.

Heterogenous Chiplet-Based Architecture

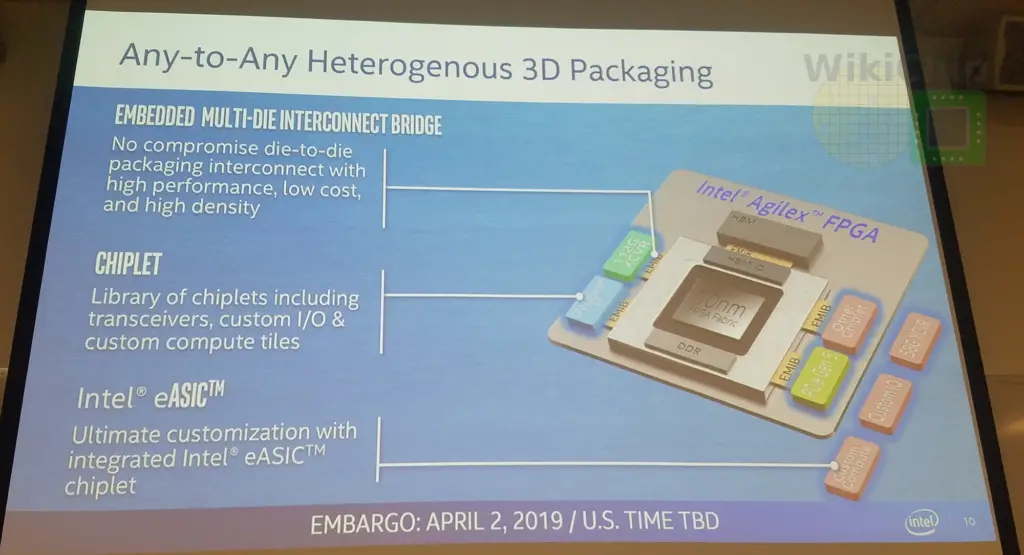

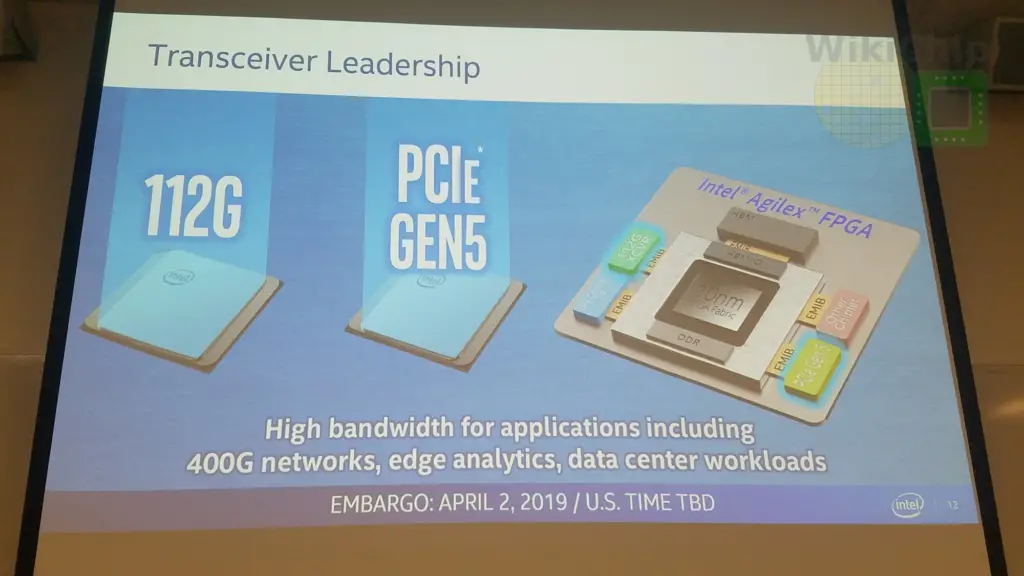

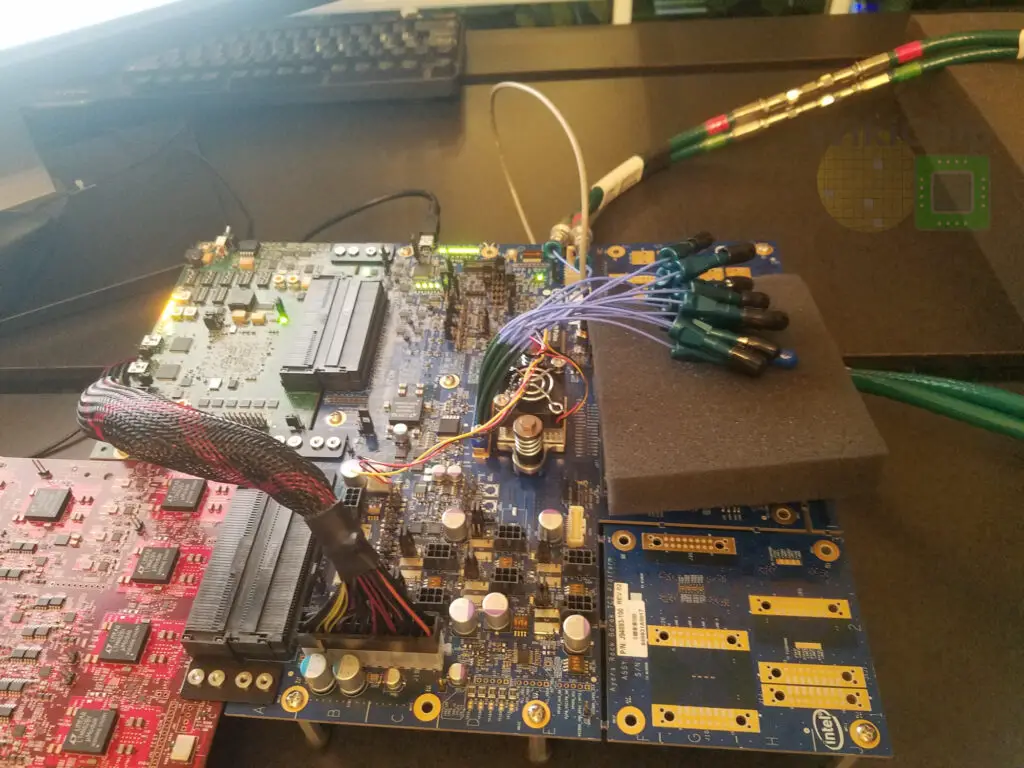

Agilex FPGAs are 2.5D system in a packages (SiP). The main FPGA die is manufactured on Intel’s 10-nanometer node. All the remaining components are individual chiplets which need not be fabricated on 10nm or on Intel’s own process entirely. The individual chiplets are in turn connected to the main FPGA die over Intel’s 2.5D EMIB technology. Though it’s a little early to see where things are heading, Intel intends on providing a predefined library of chiplets such as PCIe, HBM, and other various transceivers. Additionally, through their eASIC acquisition, the company intends on providing greater flexibility by integrating eASIC flow into its product offering.

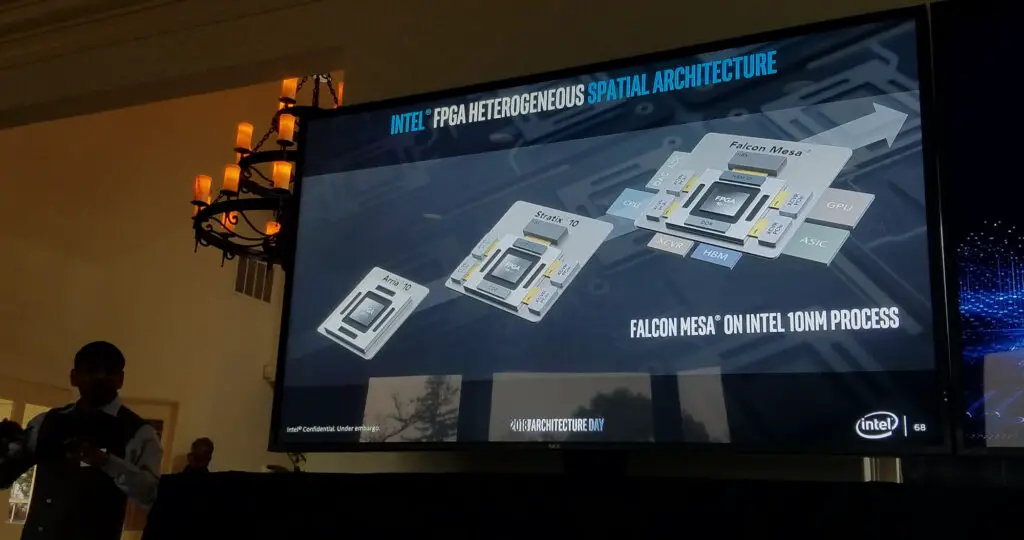

At Intel’s Architecture Day which was held late last year, we got some insight as to the direction of Intel’s PSG (programmable solution group). Ravi Kuppuswamy, Intel’s PSG VP and GM, said Intel was looking to tightly integrate their FPGAs into Intel’s portfolio. Falcon Mesa, now branded Agilex, is designed to complement Intel’s current CPUs and future GPUs and NPUs. If you look at the Arria 10 FPGAs, those integrated everything on a single die. Over the last two years, the company moved to Intel’s 14-nanometer technology for the Stratix 10 and is their first generation of heterogeneous spatial architecture. For the Stratix 10, the main FPGA block with most of the additional components were still integrated together on a single die, but this time, the transceivers were manufactured separately and were integrated using an EMIB on-package to form the final FPGA. What Intel has been working on for Agilex FPGAs is further de-integration of components. By breaking down the I/O and other secondary components, Intel plans on quickly iterating over those dies in order to expedite the time-to-market of new protocols and PHYs. This design has a couple of other benefits including a stable base design using an existing FPGA block and a rapidly improving core, GPU, transceivers, and any other ASICs. Kuppuswamy noted that Intel is building a full library of tiles including CPUs, GPUs, and HBM tiles. Tiles can then be more quickly integrated using their EMIB technology.

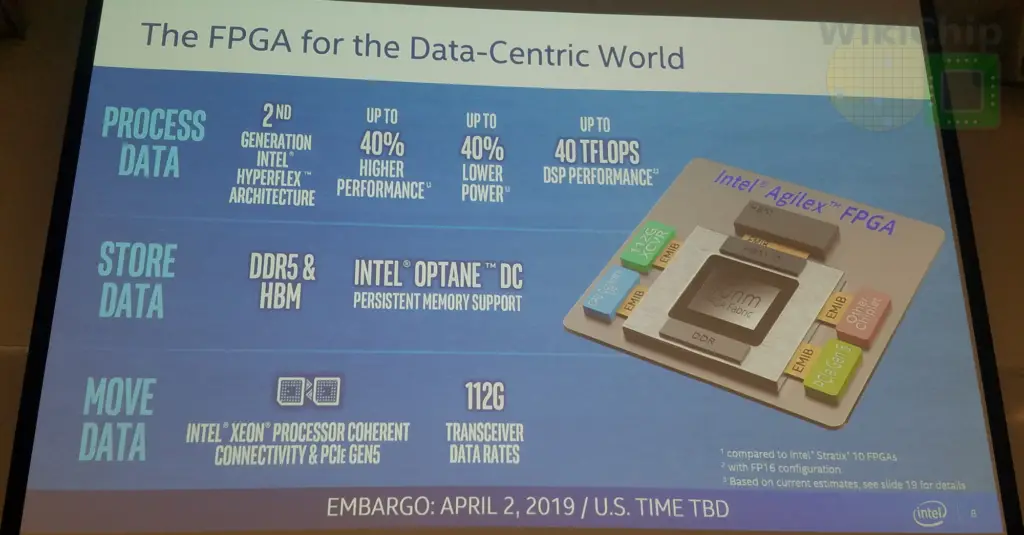

Intel isn’t ready to delve into any major details but says that Agilex FPGAs will offer up to 40% higher performance (Fmax) compared to current Stratix 10 devices or up to 40% lower total power for the same design. Agilex initial models will have PCIe Gen 4, Gen 5, DDR4, DDR5, and 112G transceivers among other options.

At Architecture Day, Kuppuswamy did provide some more insight into the performance and power we might expect from Agilex. At the bottom tier is the 20-nanometer Arria 10 FPGAs which are largely considered a mid-range FPGAs. Complementing the high-end of the spectrum are the 14-nanometer Stratix 10 FPGAs. Kuppuswamy stated that with Falcon Mesa, Intel expects to cover the entire power range – spanning all the way from low power to the highest performance with roughly a 1.5x performance jump over Stratix 10 at the high end.

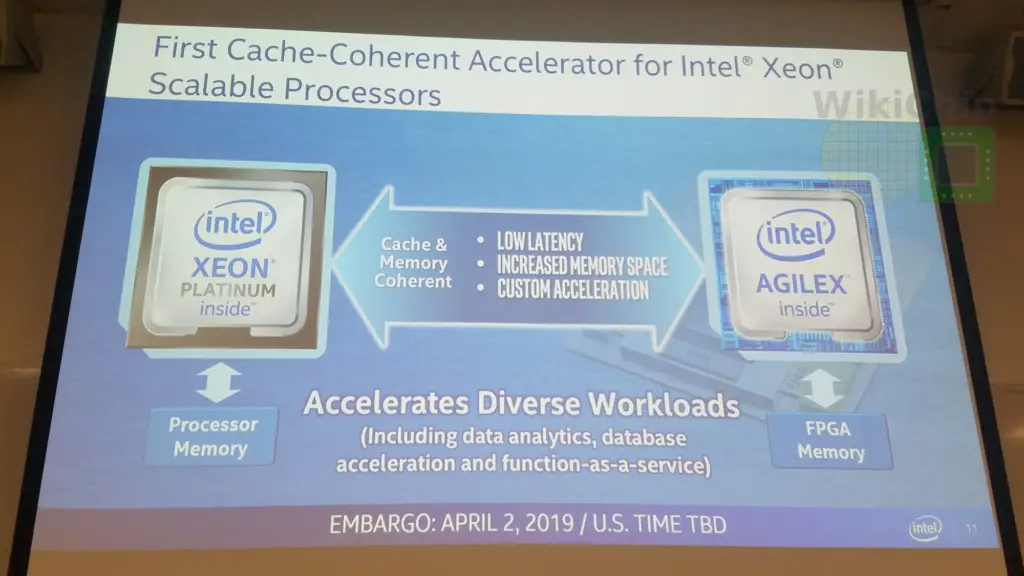

Agilex & Xeon

Intel is already shipping Xeon with integrated Arria 10 GX 1150 FPGA on the Xeon Gold 6138P so it’s no surprise that Intel is looking to expand on that. Intel plans on offering Agilex FPGAs as a cache-coherent accelerator for Intel Xeon Scalable processors. Initial products are expected to make use of UPI but early last month the company announced the Compute Express Link (CXL) interconnect technology and the formation of the consortium. Though Intel isn’t ready to confirm any products yet, we expect Agilex FPGAs to eventually make use of CXL.

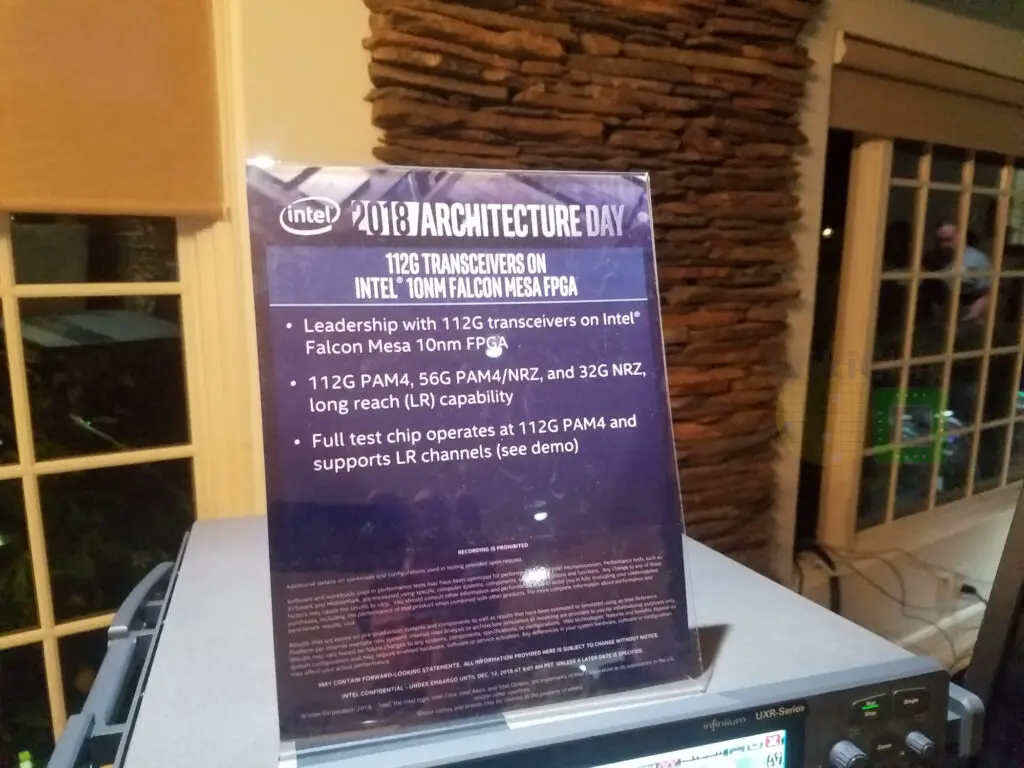

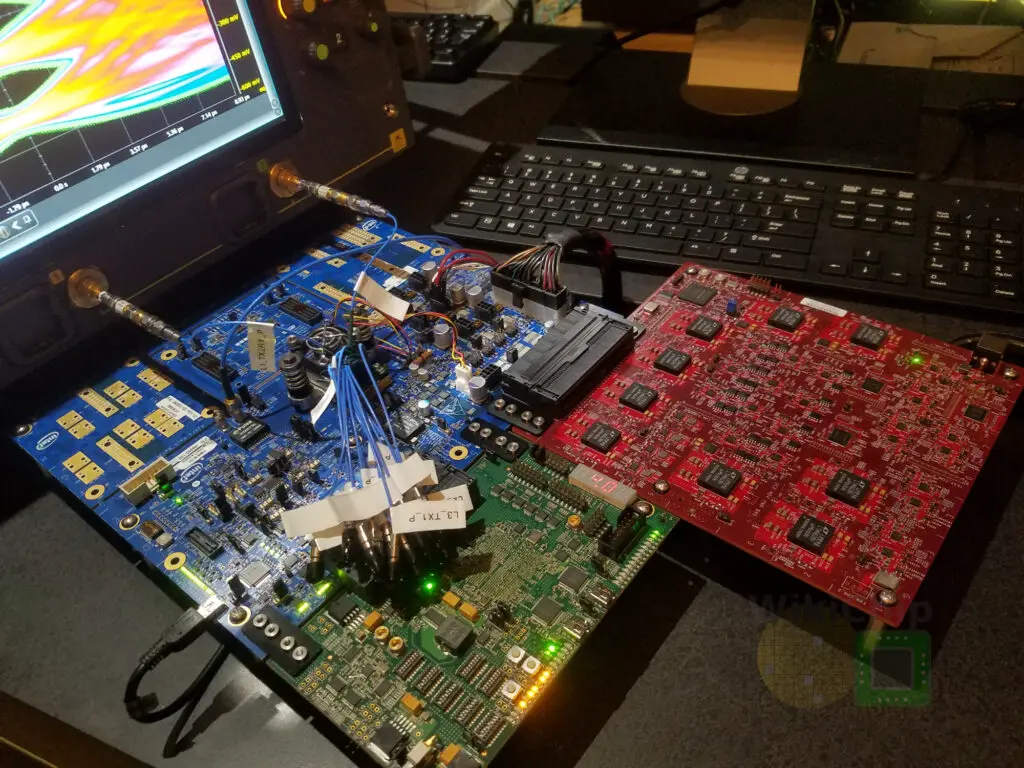

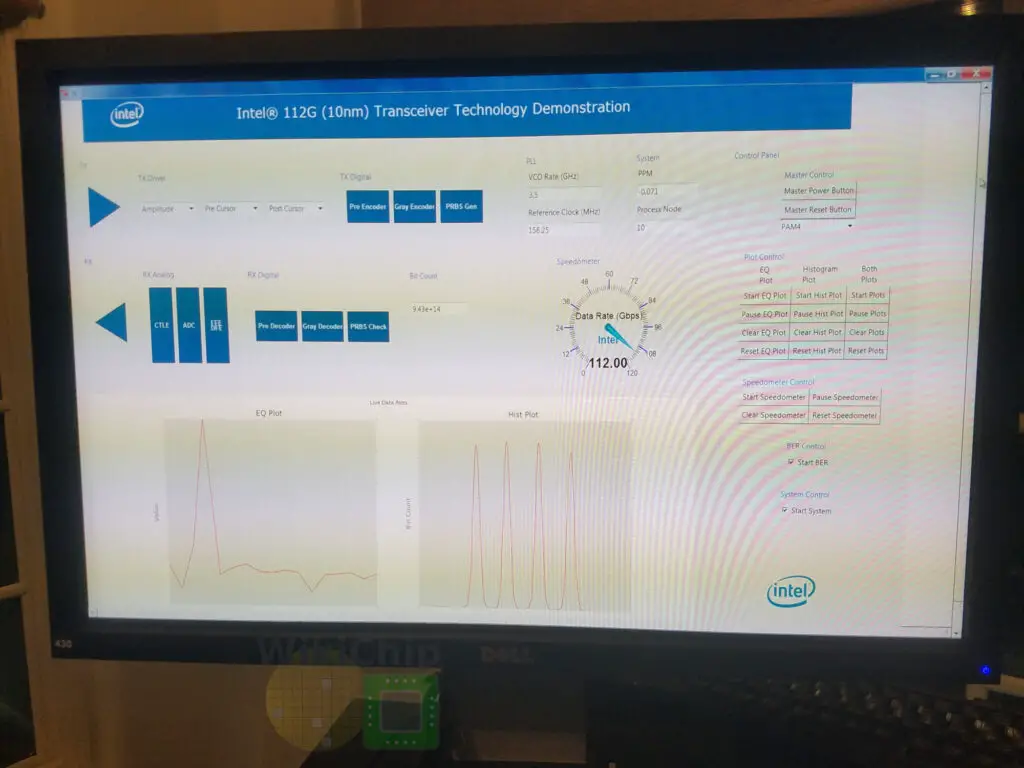

Transceivers

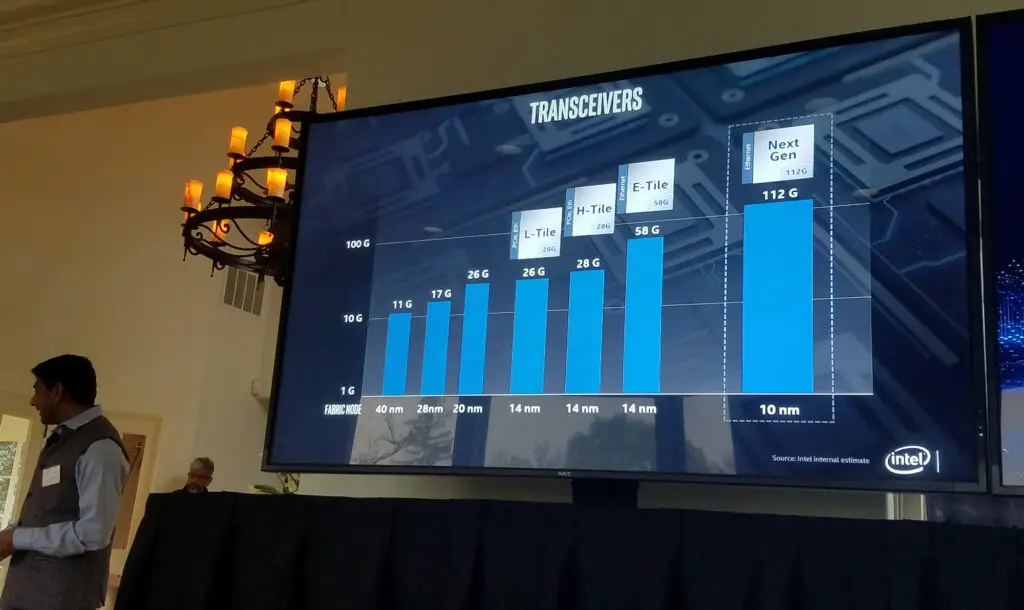

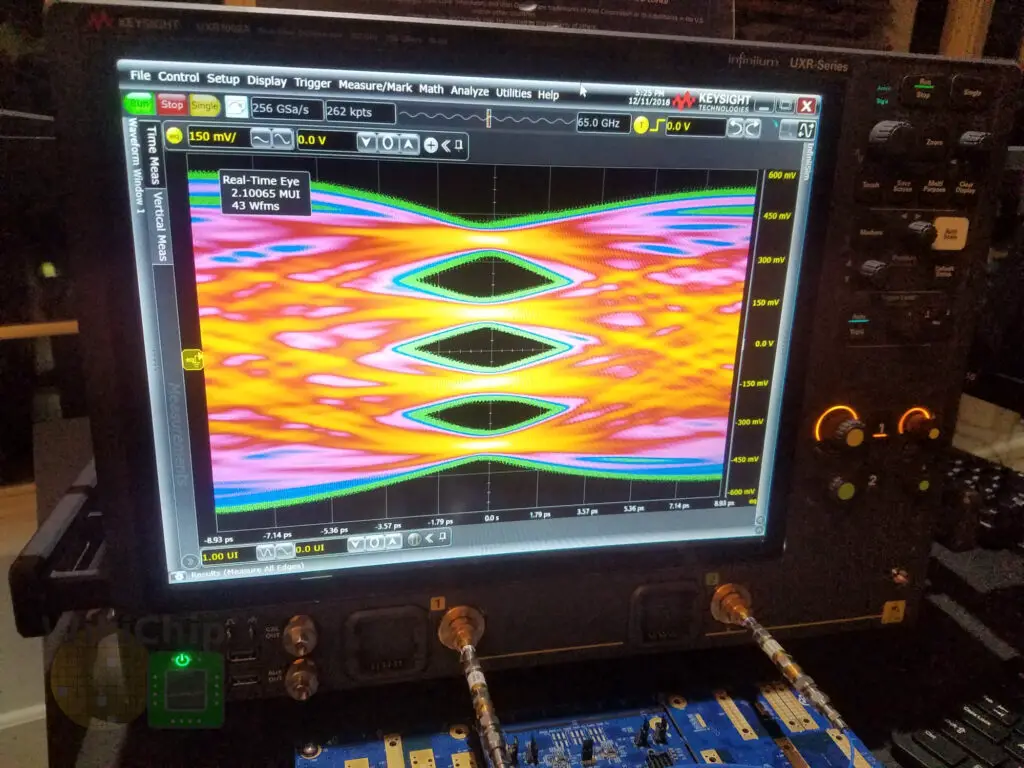

Historically, Intel/Altera used monolithic transceivers from the 40 nm to the 20 nm node. When they switched to 14-nanometer with the Stratix 10, the transceiver tiles are no longer part of the FPGA monolithic die itself but rather an independent chiplet. Currently, the company ships 58G transceivers with their FPGAs in mass production. With the use of chiplets, they are hoping to accelerate iterating on transceiver tiles.

|

|

|

|

With today’s announcement, Intel is promising to jump right to PCIe Gen 5 as well.

Agilex FPGA Family

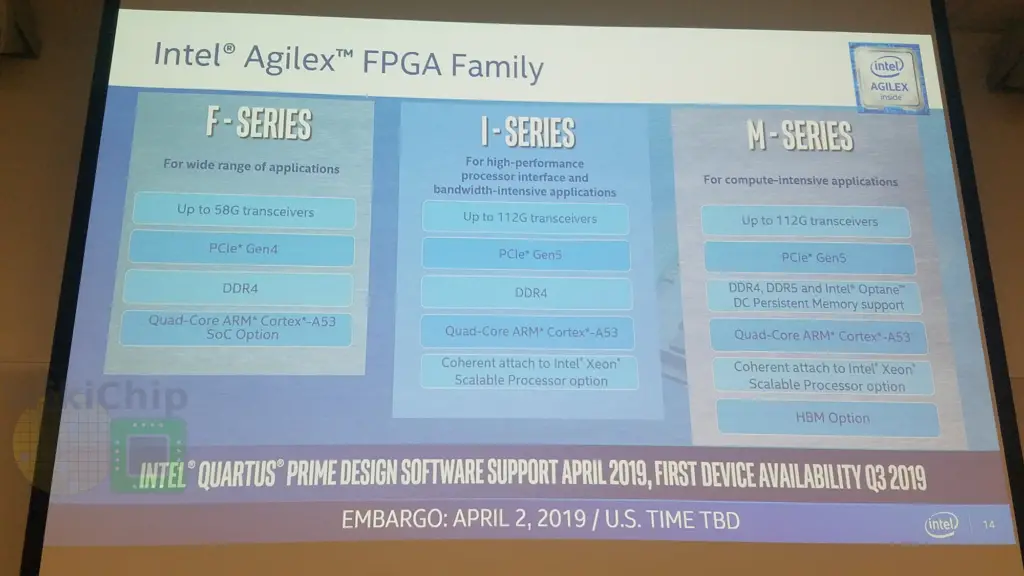

Three Agilex FPGA series are being announced – F Series, I Series, and M Series.

Availability

Agilex FPGAs will start sampling in the second half of 2019.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–