Intel Announces 20Å Node: RibbonFET Devices, PowerVia, 2024 Ramp

Today Intel held its global Intel Accelerated event where the company revealed a detailed process and packaging technology roadmap for the next half-decade. At the event, the company unveiled a number of new process nodes. Among some of its new disclosures is the Intel 20A node.

This article is part of a series of articles covering Intel’s 2021 Accelerated Event:

- Intel 2021 Process Technology Update

- Intel Announces 20Å Node: RibbonFET Devices, PowerVia, 2024 Ramp

- Intel Unveils Foveros Omni And Foveros Direct; Leveraging Hybrid Bonding

Intel 20A

Today Intel unveiled its “Intel 20A” node (A for Angstrom). The naming itself is largely superficial and is intended to denote further scaling from “Intel 3” rather than any actual feature size. Like Intel 3, Intel 20A will also be an Intel Foundry Services node offered to customers. With Intel 20A, the company is introducing a number of major innovations which set it apart from all recent prior Intel nodes. “Intel 20A will be another watershed moment in process technology when we introduce it in the first half of 2024,” said Dr. Ann Kelleher, senior vice president and general manager of Technology Development. While Intel isn’t disclosing too many technical details, the few high-level teasers they did disclose make this process technology extremely interesting.

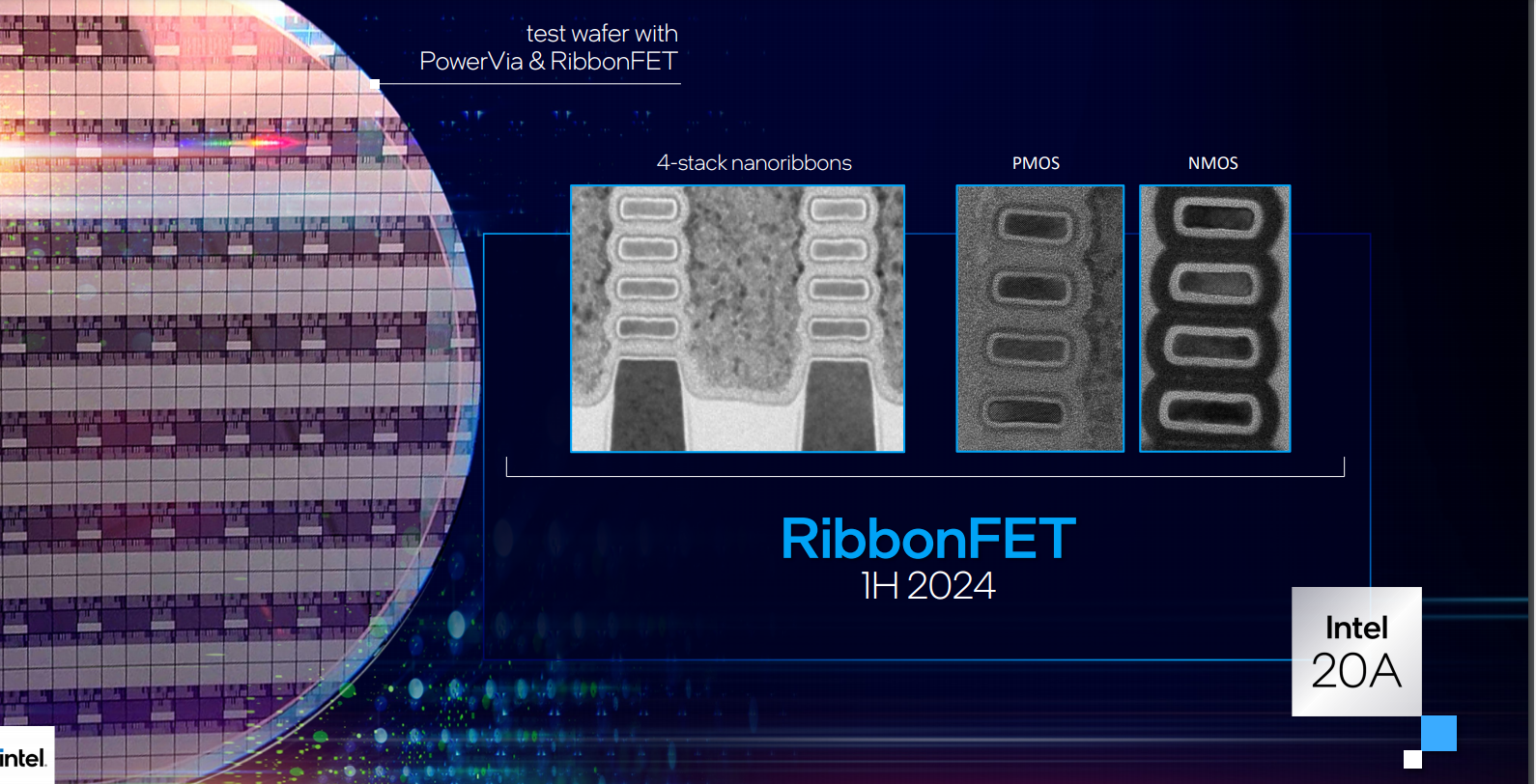

Since the 22-nanometer node, Intel has been utilizing the FinFET transistor architecture for all its nodes. The 3D structure of a FinFET device improves the crossectional area of the gate which helps improve drive current while enabling further area scaling. There has been a lot of discussion over the past few years of when we can expect to see Intel moving to a new device architecture as FinFET starts running out of steam. At today’s Intel Accelerated event the company revealed that Intel 20A will make use of a new device architecture the company calls “RibbonFET” which is their implementation of a Gate-All-Around Field-Effect Transistor or GAAFET.

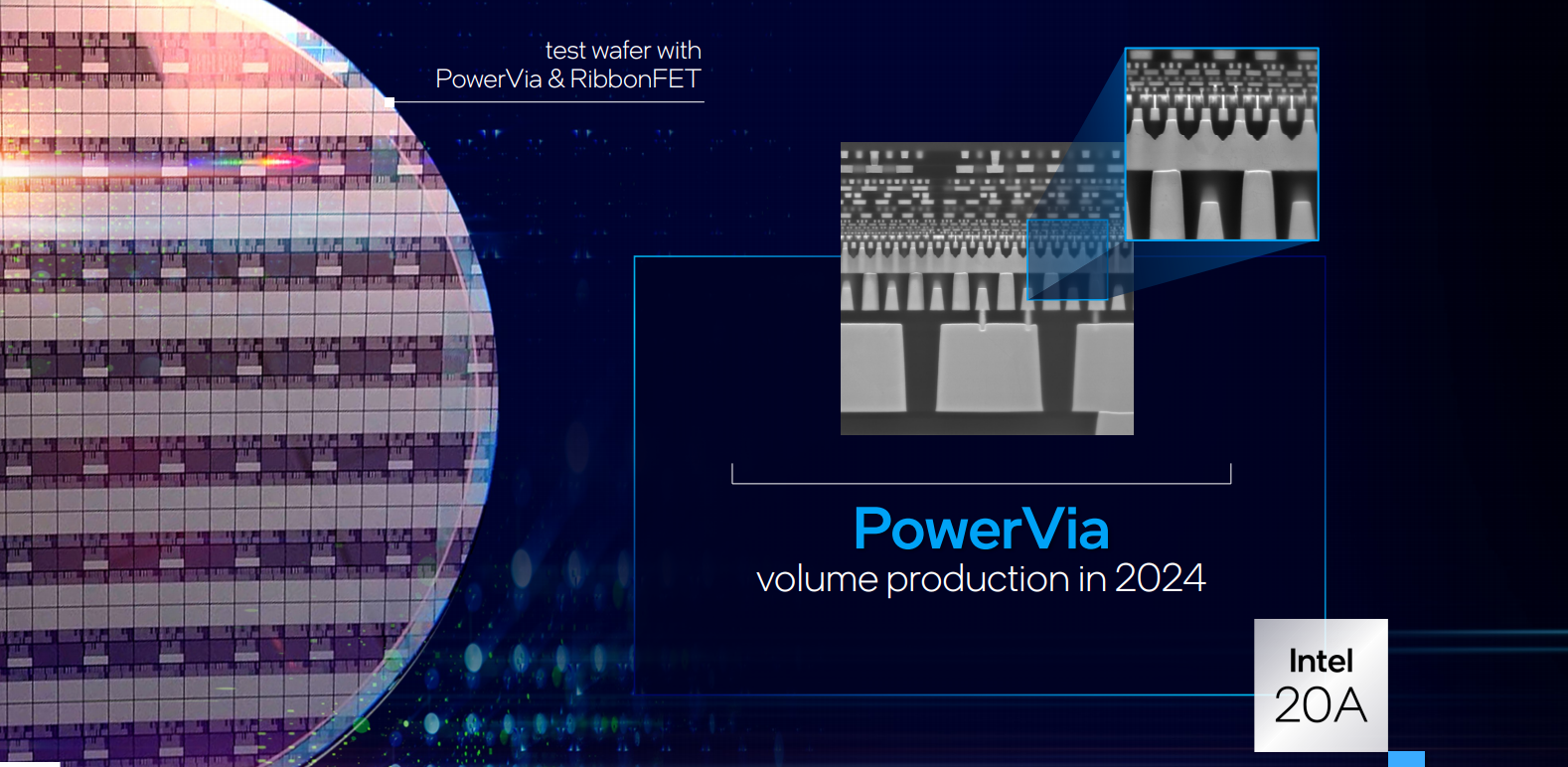

The second major technology introduction with the Intel 20A node is what they are calling “PowerVia”. PowerVia is a back-side power-delivery network (BS-PDN). While traditionally, the power delivery network along with signal routing all utilized the same standard metal stack on top of the transistor, Intel’s PowerVia technology refers to a new on-die power delivery scheme whereby all power delivery networks are removed from the top interconnects and are moved to the bottom – physically below the actual active devices. Here, the power delivery network connects directly to the transistors without going through the interconnect stack. “This is a unique technology developed by Intel engineers that will make its debut in Intel 20A. Traditional interconnect technology connects on top of the transistor layer. With the result of intermixing power and signal wires, routing inefficiencies arise hampering both performance and power. Our solution is a novel process where the power wires are placed underneath the transistor layer – on the backside of the wafer.” said Dr. Sanjay Natarajan, SVP and Co-General Manager Logic Technology Development.

If we go by public work presented by Imec, this is done by having the power delivered on a separate wafer which is then bonded to the thinned-down carrier side of the active wafer. Intel says PowerVia effectively eliminates droop. With thick power interconnects on the backside, resistance can also be reduced. There are possibilities for introducing other components such as MIM caps. “By eliminating the need for power routing on the front side of the wafer, more resources become available top optimize signal routing and reduce delay. This also enables better power delivery by reducing droop and lowering noise. This allows us to optimize the performance, power, and area depending on the product needs. We have been perfecting this process over the last several years and PowerVia will be an industry-first deployment for the backside power delivery network,” he added. “As we look to productize this innovation, our defect density, performance, and reliability give us confidence that it will be ready to ramp into production. In fact, we expect to test PowerVia on earlier nodes to ensure this groundbreaking technology is fully ready before it ramps in volume in Intel 20A in 2024.”

PowerVia will first be implemented in Intel 20A where the entire power delivery network will be integrated on the backside, connecting directly to the transistors without going through the interconnects above. The entire interconnect stack will be available for signal routing, allowing for either denser routing or faster routing (depending on the logic design choice).

Intel expects Intel 20A to ramp in 2024, bringing their process technology to parity-or-better than foundry products.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–