Left, Right, Above, and Under: Intel 3D Packaging Tech Gains Omnidirectionality

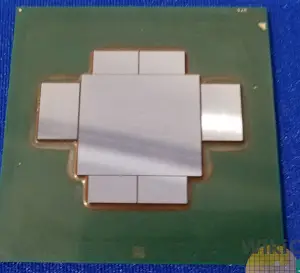

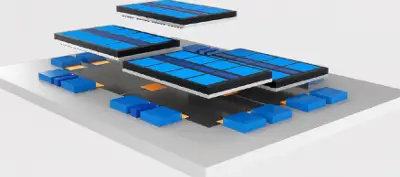

A look at ODI, a new family of packaging interconnect technologies that bridges the gap between Intel’s EMIB (2.5D) and Foveros (3D) by providing the flexibility of an EMIB in 3D with additional benefits of thermal & power.

Read more