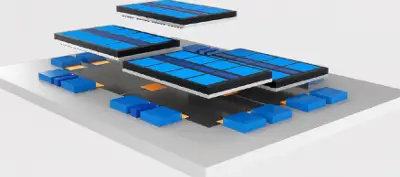

Intel Introduces Co-EMIB To Stitch Multiple 3D Die Stacks Together, Adds Omni-Directional Interconnects

Intel is expanding its packaging portfolio with more advanced 2.5D and 3D technologies including multiple 3D stacks and omnidirectional interconnects.

Read more