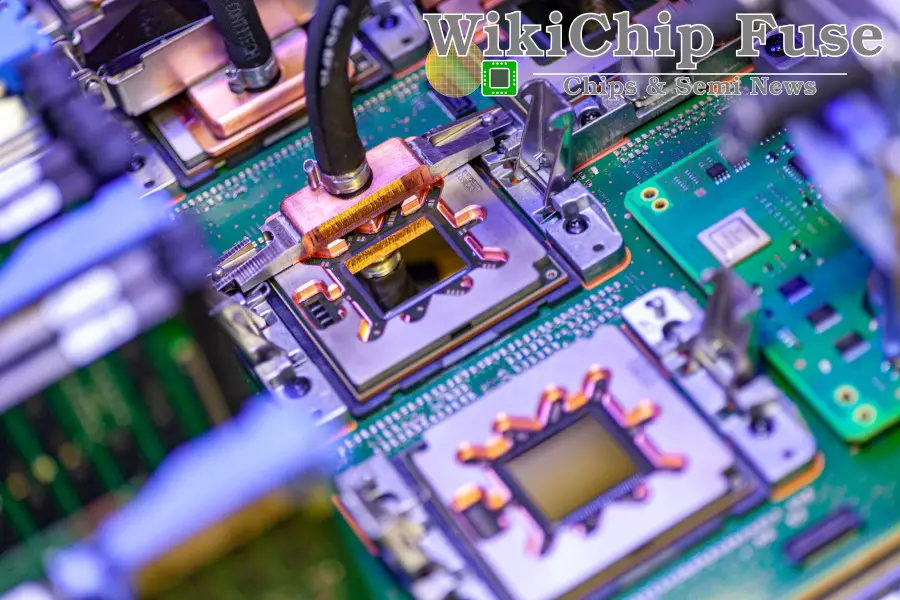

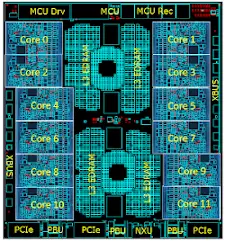

IBM Doubles Its 14nm eDRAM Density, Adds Hundreds of Megabytes of Cache

IBM doubles its 14-nanometer eDRAM density through physical design work, enabling the packing of hundreds of additional megabytes of cache on the latest z15 microprocessor and system controller.

Read more