A Look at Intel Lakefield: A 3D-Stacked Single-ISA Heterogeneous Penta-Core SoC

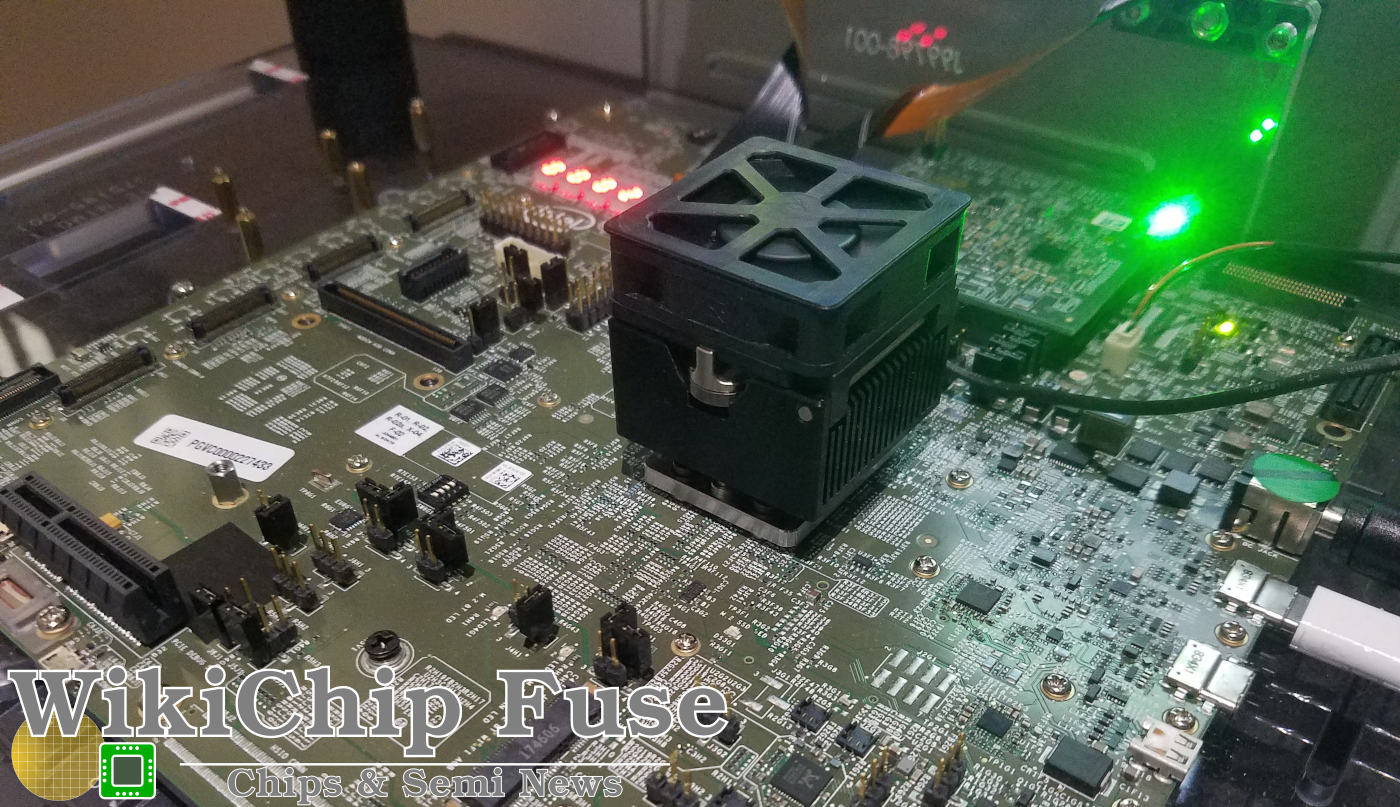

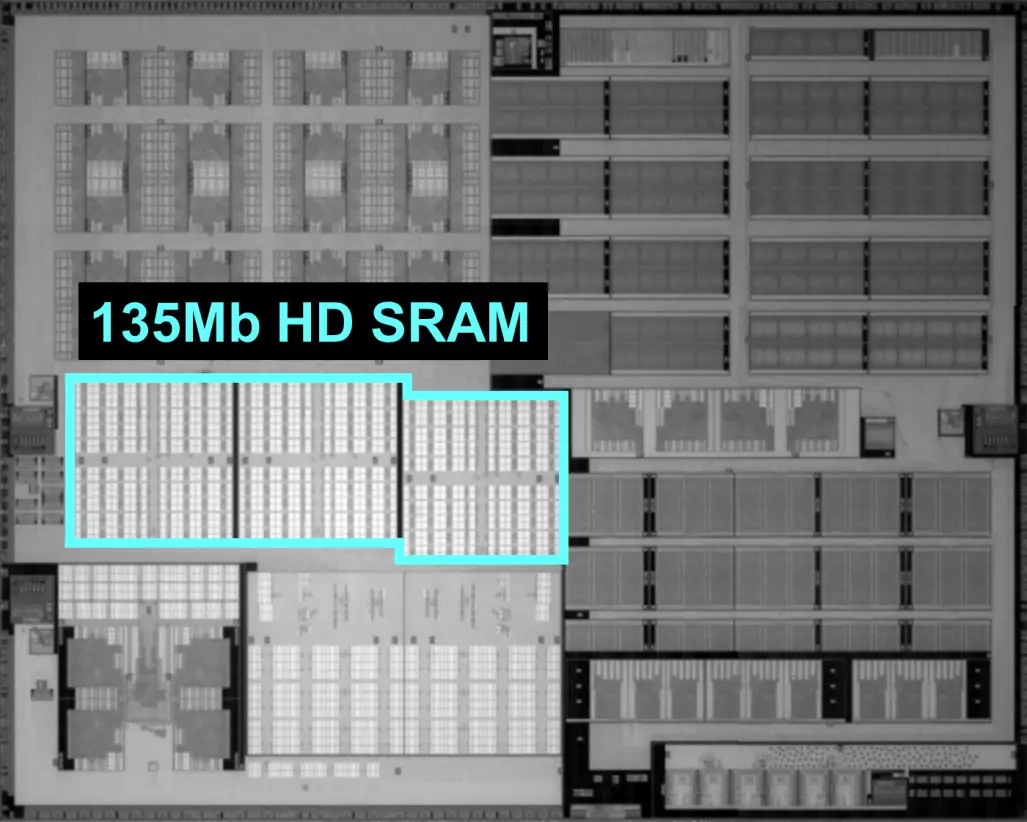

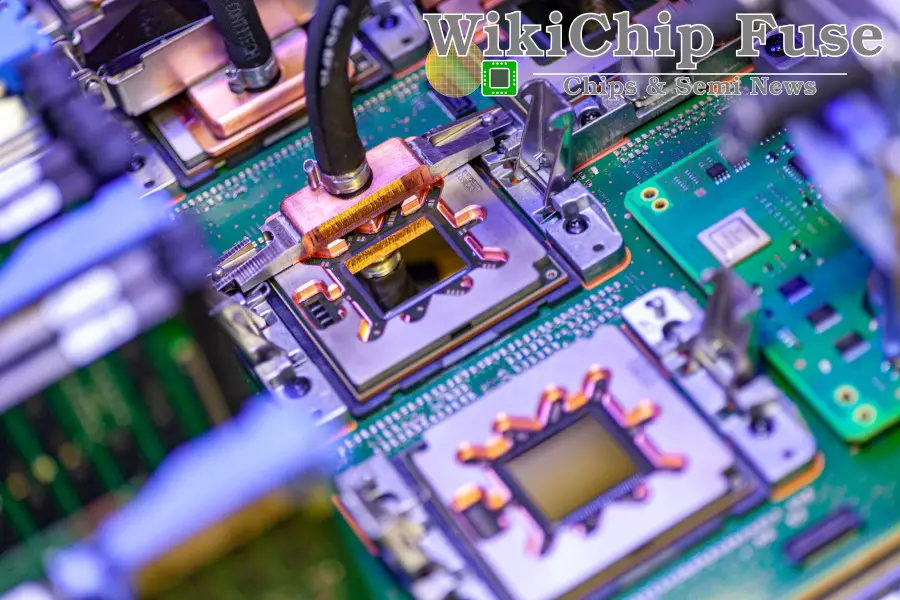

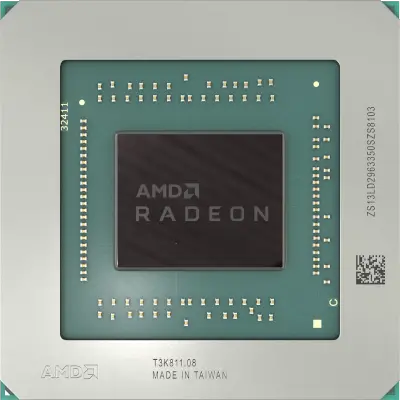

A look at Lakefield, Intel’s new mobile-class heterogeneous penta-core SoC built using two dies 3D-stacked face-to-face using the company Foveros packaging technology.

Read more