Hot Chips 30: Intel Kaby Lake G

Cross-SoC DPTF

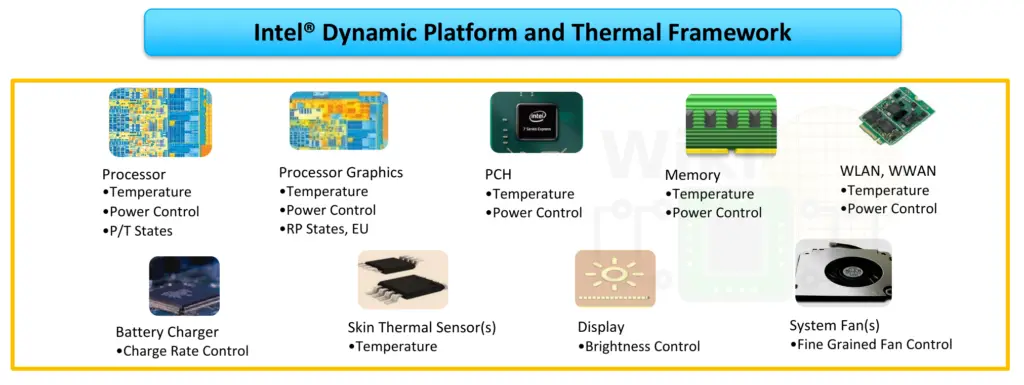

Dynamic Platform Thermal Framework (DPTF) is not new but around Broadwell a couple of new enhancements came about including better support for external SoCs. The goal of DPTF is to create a heuristic model of everything that’s going on at the platform level in order to manage the static and dynamic power of the chip to maximize performance where it’s needed. For this to work effectively, all components in the system are finely monitored and controlled in order to minimize the power consumption when not needed and maximize it when it is, all within the thermal constraints of the system.

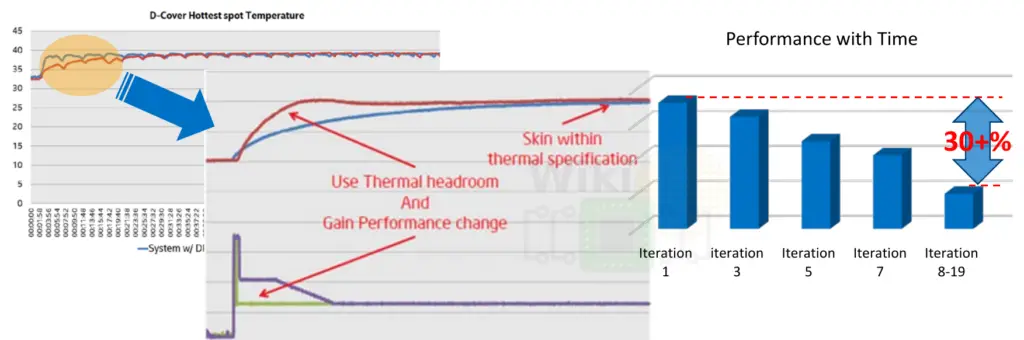

DPTF works very much like other Intel technologies that improve performance by taking advantage of the available headroom such as TSKIN in the case of mobile and fanless designs. Since this works at the platform level, it’s taking into consideration other components such as memory, the chipset, wireless LAN, and I/O. Taking advantage of this, Intel claims that DPTF can delivery up to 30% performance increase on cold systems.

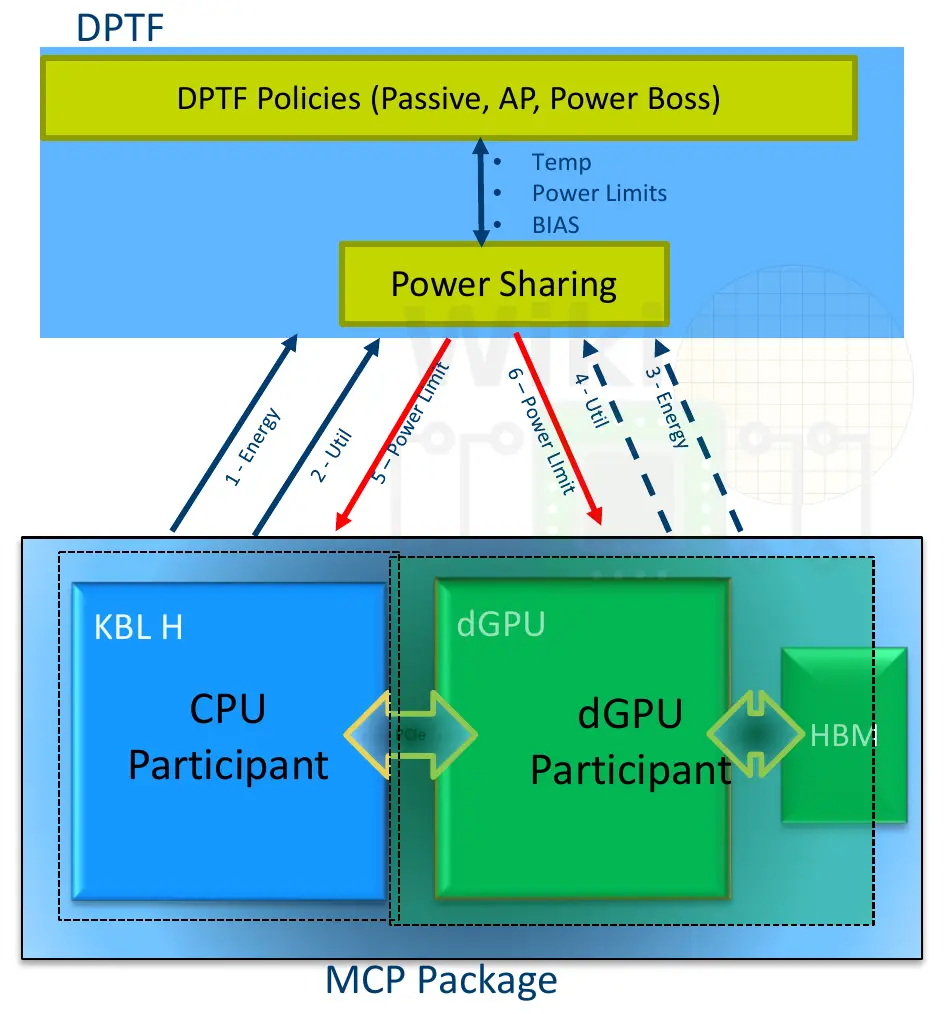

To aid system designers, DPTF provides additional hooks in the form of power budgets that each of the external chips adheres to as well as the various power policies that they can implement. This allows external chips to use the unified platform power management control mechanisms, taking advantage of the available power, temperature, and fan speed much in the same way the central processor can. With Kaby Lake G, the new on-package discrete graphics was added to DPTF in the same way.

The problem with Kaby Lake G is that the GPU actually does not expose any of those power management controls via a shared interface. In fact, the only available interface is the PCIe 3 connection. To solve this Intel implemented a software-based power management control. The package is divided into two main power domains: one for the Kaby Lake H processor and one for the discrete GPU and the HBM. Each domain autonomously manages its own individual budgets on a ~100ms control loop (for the GPU this is managed by the software). The final platform (overall MCP power budget) is handled by a hardware control logic. A PID controller makes the final decision as far as the full package power available headroom.

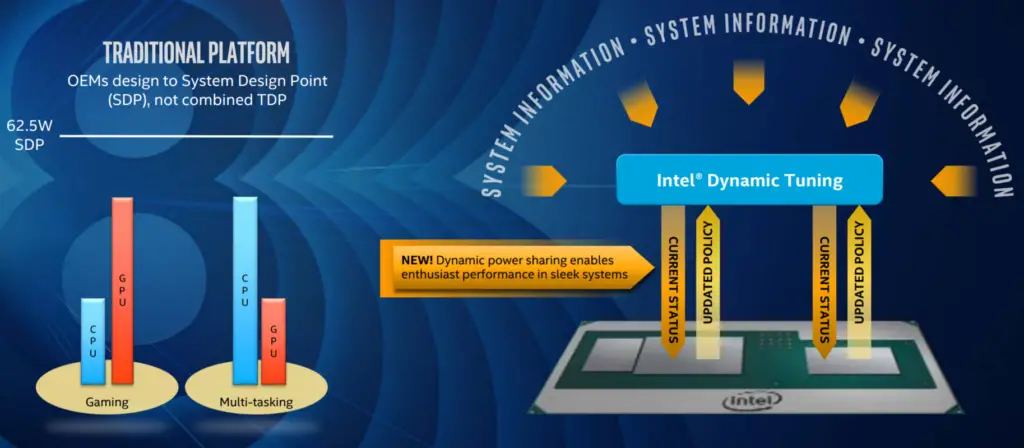

In thin mobile and fanless solutions, normally, system designers will allocate a certain fixed power for the central processor and a certain fixed power budget for the graphics. The sum of both are within the full system thermal envelope constraints the device is designed for. However, this kind of design makes worst-case assumptions about the system. In practice, systems seldom reach the absolute allowed budget for both components at the same time. More often, this extra thermal budget is left untapped.

With Kaby Lake G, this extra thermal is better shared between the CPU and GPU. Intel claims that the fine-grained sharing of the overall power budget results in the upfront design benefit of 17.5 W for the same level of performance. This gives the OEM the flexibility of choosing between higher performance or lower power.

Happy Marriage of Technologies and Designs

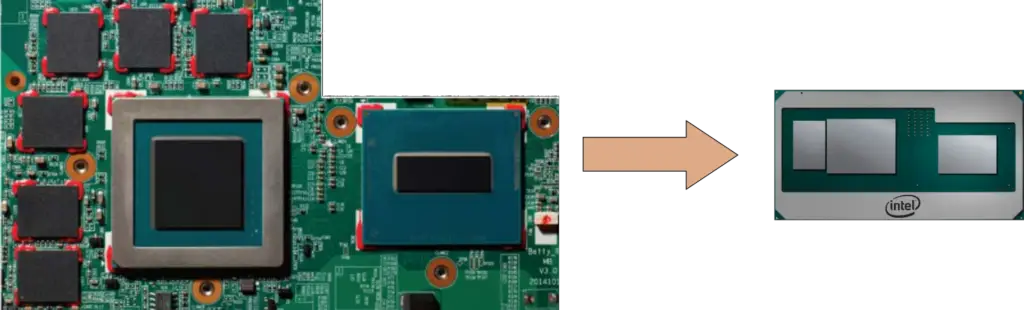

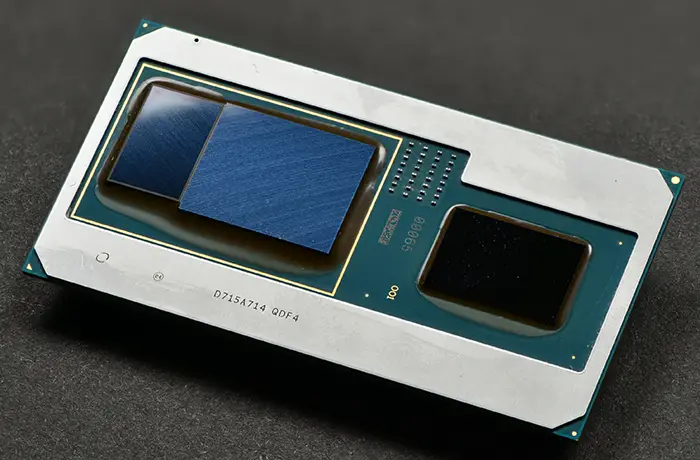

The combination of a semi-custom GPU die from AMD and the Intel processor resulted in a fairly unique product. The use of an existing Intel design and a semi-custom GPU from AMD made the quick time to market possible. In fact, Chennupaty mentioned going from project approval time to final product took just four and a half quarters. In many way, Kaby Lake G offers the best of both worlds. From a performance and power perspective, Kaby Lake G better shares its power budget, shifting resources where needed which results in either lower power or higher performance depending on the design point. From a form-factor perspective, Kaby Lake G cuts down on the board space required. From a traditional CPU + GPU + GDDR5 memory to a Kaby Lake G-based design, Intel claims that around 1,900 mm² of board space is saved.

This article is integrated into the following main WikiChip article: Kaby Lake Microarchitecture § Kaby Lake G, Kaby Lake G.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–