A Look At Intel 4 Process Technology

Scaling Is DTCO-Heavy

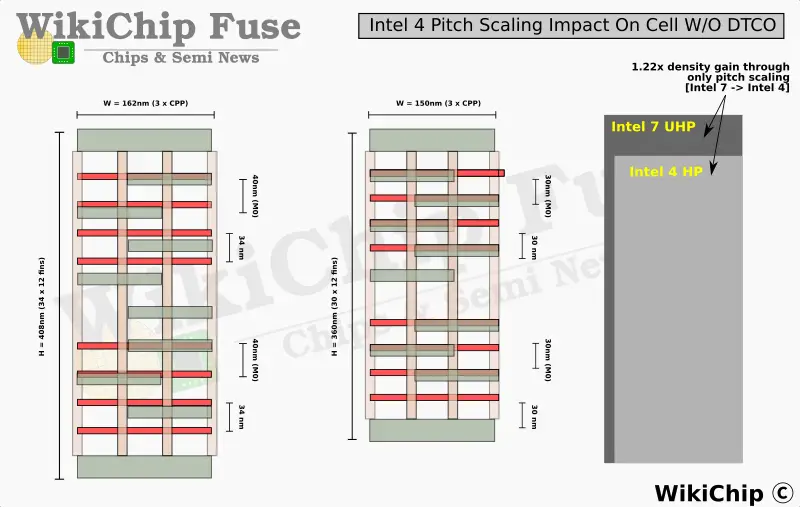

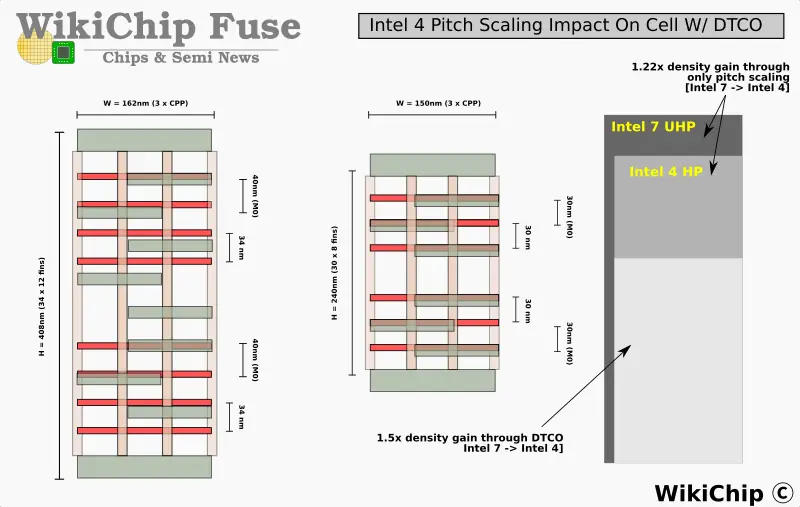

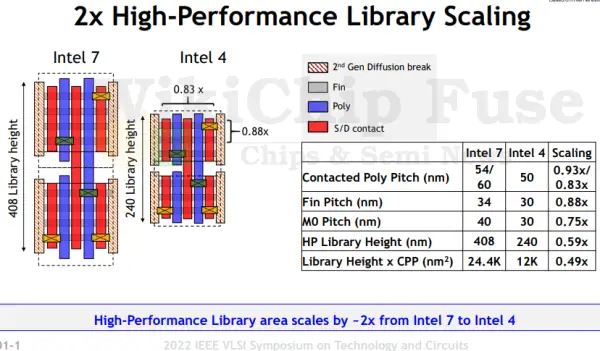

As we’ve seen over the last few nodes, the targeted PPA goals now heavily involve DTCO. Intel 4 is no exception. In fact, if we transpose Intel 7 cells onto Intel 4 and adjust for pitches only, we’d get a 1.22x transistor density improvement or roughly 0.82x scaling. That implies that instead of pitch scaling, DTCO accounts for the vast majority of the density improvement in Intel 4.

A number of key technologies are at play here. First Intel 4 utilizes second-generation COAG and second-generation single dummy gate, allowing them to scale with the new gate and fin pitches while maintaining the cell height and cell width advantages that enabled the density improvement we saw in Intel 7. Previously, Intel had two diffusion lines worth of spacing at the area between the nMOS and pMOS devices (the former contact area for the gate input). Intel 4 exploits this region of the cell and eliminates one of that diffusion lines, shorting the cell height and gaining valuable space. We estimate that this alone produced around 11.5% more area scaling. Finally, due to its higher performance, Intel 4 underwent a 4:3 fin depopulation. This was the single largest contribution to the overall area shrink at an additional 25%. All in all, DTCO adds a whole 1.5x scaling on top of traditional pitch scaling. This is a testimony to the importance of DTCO in modern leading-edge nodes and how STCO will play an even bigger role with the introduction of future technologies such as buried power rails and backside power delivery networks.

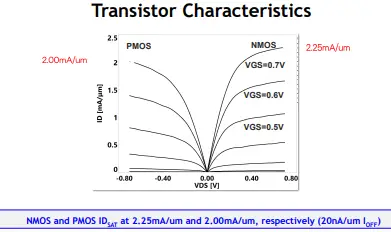

In order to facilitate fin depopulation, device performance must be enhanced. For Intel 4, the company reported drive currents exceeding 2mA per micron for both nMOS and pMOS. Drive current of 2.25 mA per micron for nMOS at 0.7 V and a leakage current of 20 nA per micron. Likewise, for pMOS, a drive current of 2 mA per micron at the same leakage was also reported. Those numbers represent around 25-30% improvement over 10-nanometer devices.

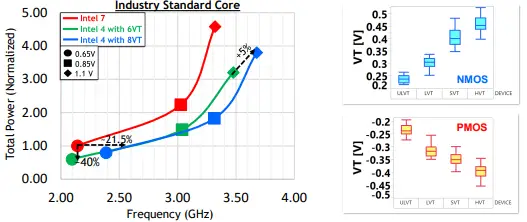

Intel 4 offers eight threshold voltage devices (4 nMOS / 8 pMOS). Those new devices offer an additional 5% power-unconstrained performance improvement over Intel 7.

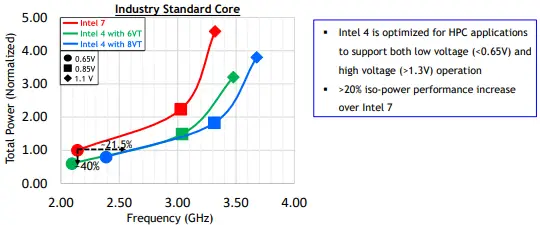

Intel also reported some power-performance numbers utilizing a standard licensable core (presumably a Cortex-A7x core). The power-frequency graph below compares the same core on Intel 7 versus Intel 4. At low voltage, Intel is reporting greater than 20% frequency improvement at iso-power over Intel 7. Alternatively, at the same low voltage, the same core results in around a 40% reduction in energy at iso-frequency.

Density

Putting everything together, Intel says that, based on internal estimates, they see a full 2x high-performance library scaling from Intel 7 to Intel 4.

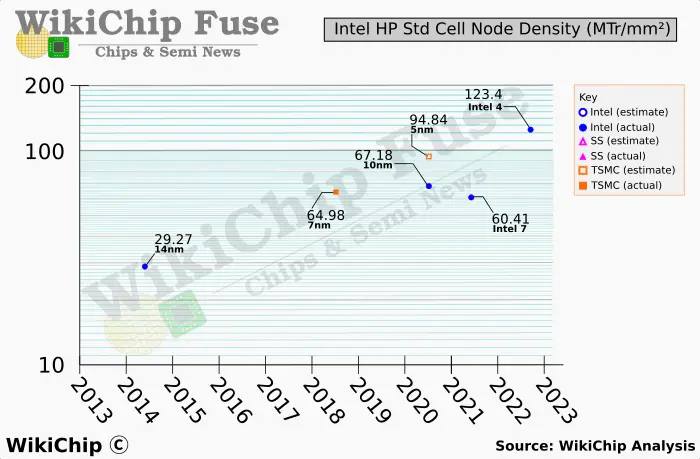

As usual, WikiChip produces its own independent estimates based on the currently publically available foundry data. Our own estimates suggest Intel 4 offers 1.83x density improvement over Intel 7/10nm. However, our estimates also suggest Intel 4 offers a 2.04x density improvement over Intel 7. So what gives? The answer is actually in Intel’s own VLSI presentation slide above. With the introduction of 10-nanometer SuperFin and its successor, Enhanced SuperFin (which is now called Intel 7), Intel introduced a new transistor with a 60 nm poly pitch for even higher drive current performance. While producing significantly higher performance transistors, it had the adverse effect of reducing logic density by exactly 0.9x. It’s worth noting that those cells are used in the Golden Cove and Gracemont cores found in Alder Lake. Because they are directly comparing their highest-performance Intel 7 transistors found in their most recent chips to Intel 4 for an apples-to-apples comparison, the density scaling numbers they are reporting are from that library.

To that end, we estimate Intel 4 at 123.4 MTr/mm², 2.04x from 60.5 MTr/mm² in Intel 7. Our data for TSMC N5 is very much incomplete but our rough estimates based on known pitches put their HP library at 94.85 MTr/mm². Based on most of the recent publically available foundry data, Intel 4 HP cells appear denser than TSMC N5 HP and are likely closer to or better than TSMC N3 HP cells and denser than Samsung’s 3GAE. Given the turmoil 10nm had on the company over the last three years, coming out of it with that kind of numbers is quite surprising. It also strongly suggests Intel 3 can match and surpass upcoming 3nm-class foundry offerings.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–