Subscriber-Only ContentView All

Our latest subscriber-only content. Our patrons enjoy early-bird access to some of our content.

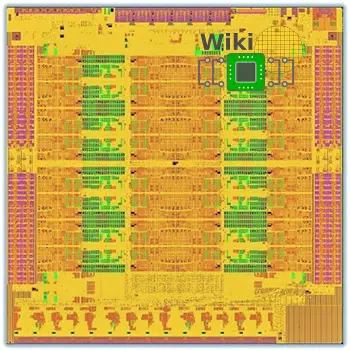

A Look At AMD’s 3D-Stacked V-Cache

[Subscription] A technical look at AMD’s 3D-Stacked V-Cache

ArchitecturesView All

Our latest coverage from the chip architecture world, including announced and planned as well as recently launched products.

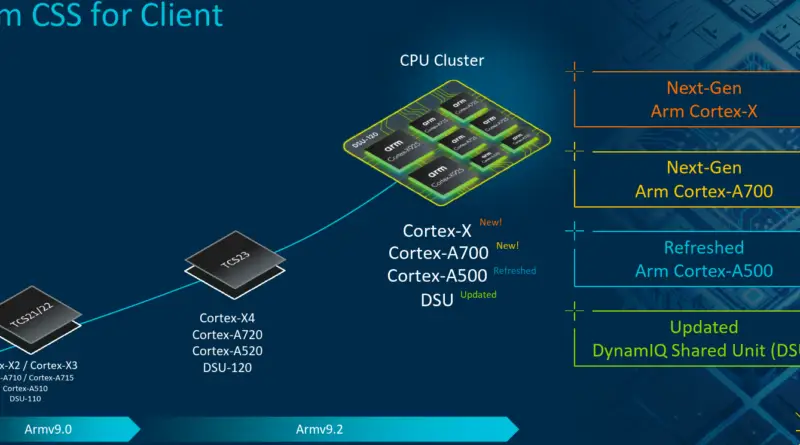

Arm Unveils 2024 Compute Platform: 3nm, Cortex-X925, Cortex-A725, Immortalis-G925

Arm unveils its 2024 Compute Platform: 3nm, Cortex-X925, Cortex-A725, Immortalis-G925

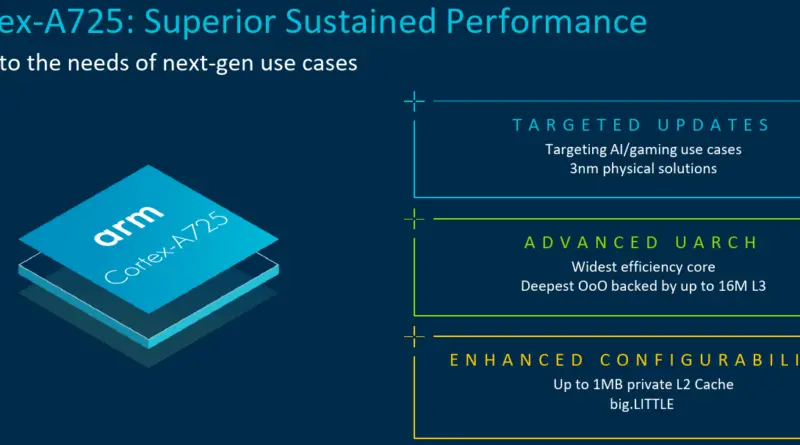

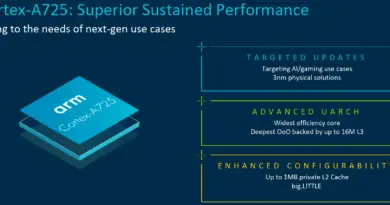

Arm Launches Next-Gen Big-Core: Cortex-A725

Arm launches its next-generation big core, the Cortex-A725

Arm Launches Next-Gen Flagship Cortex-X925

Arm launches its next-generation flagship processor, the Cortex-X925

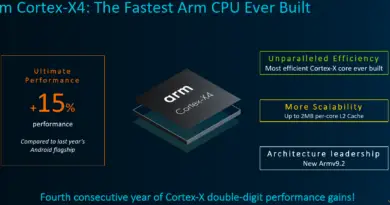

Arm Introduces The Cortex-X4, Its Newest Flagship Performance Core

Arm Introduces Its Newest Flagship Performance Core, The Cortex-X4

Process TechnologyView All

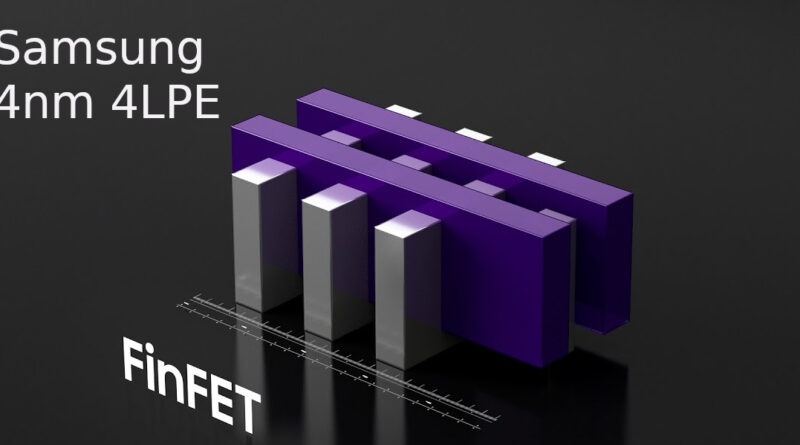

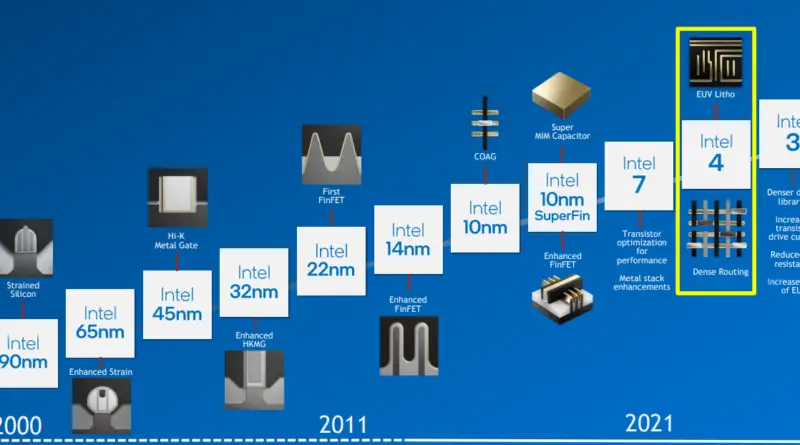

Our latest coverage from the semiconductor world including recent announcements and analysis of new process nodes from semiconductor foundries including Intel, TSMC, Samsung, GlobalFoundries, and other.

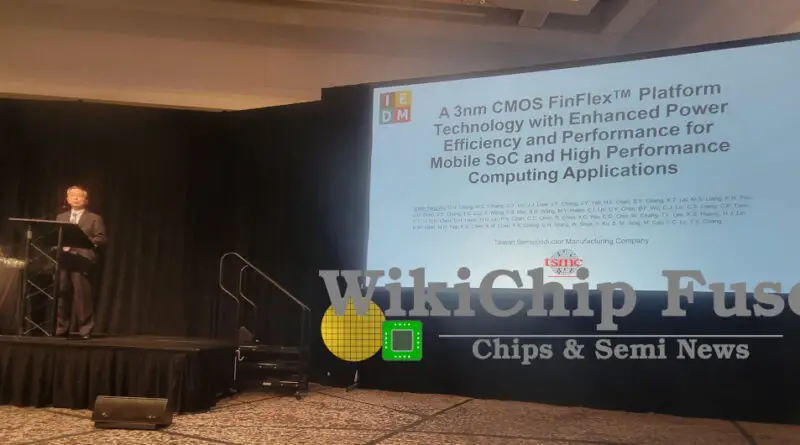

TSMC N3, And Challenges Ahead

A Look At TSMC N3 Process

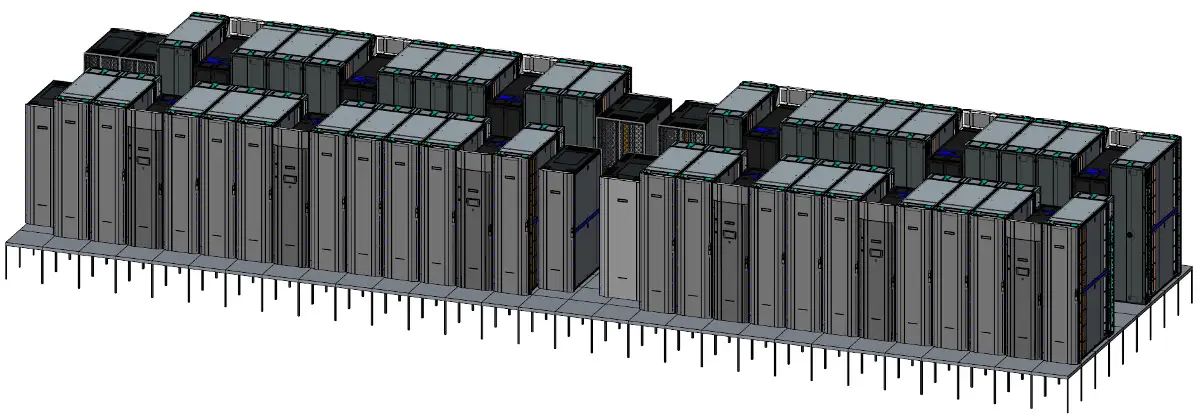

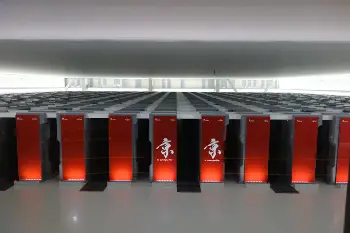

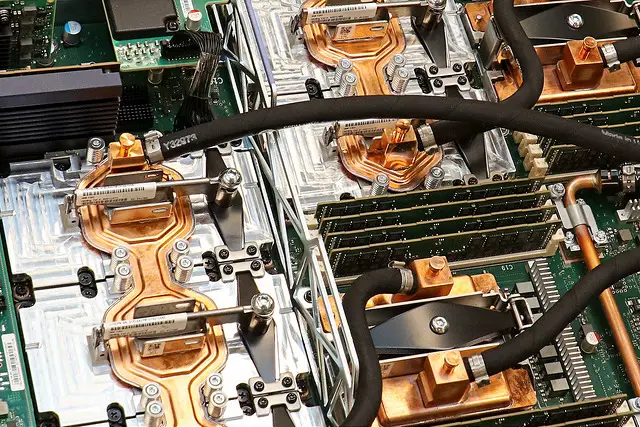

SupercomputersView All

The latest chip-related news from the world of HPC and supercomputers.