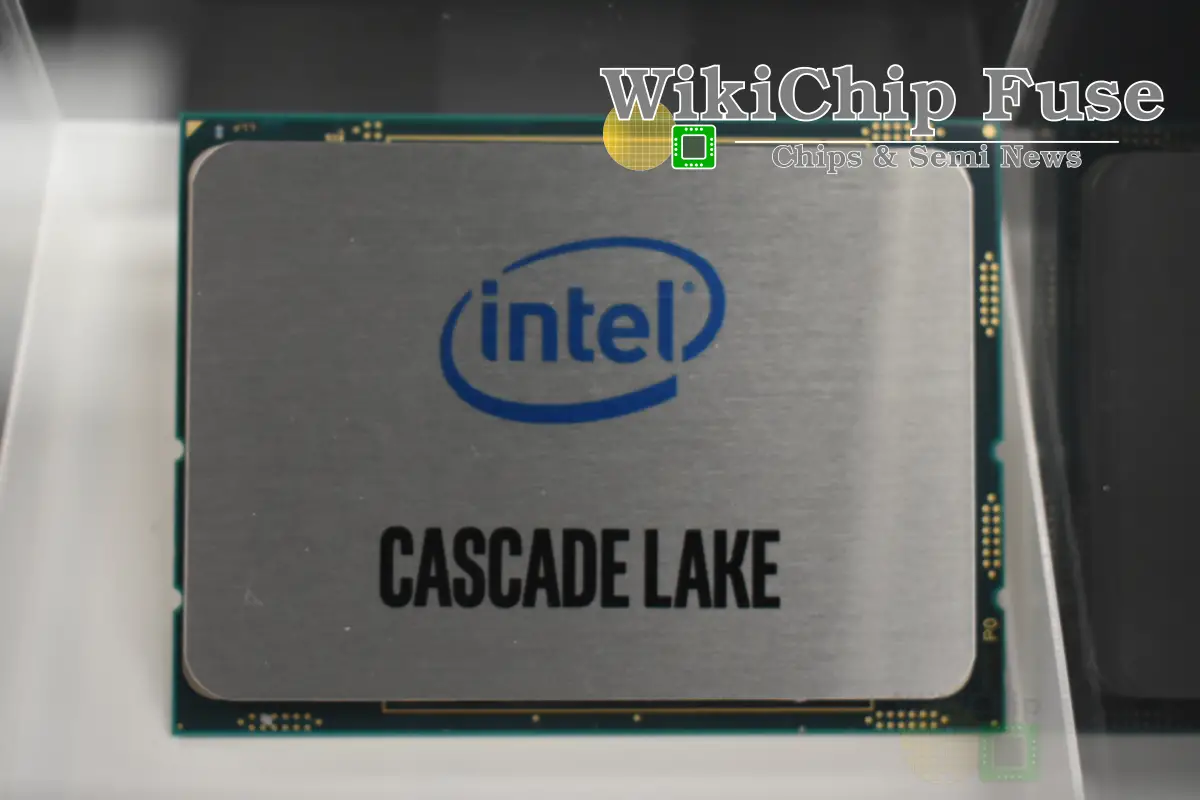

Intel Launches 3rd Gen Ice Lake Xeon Scalable

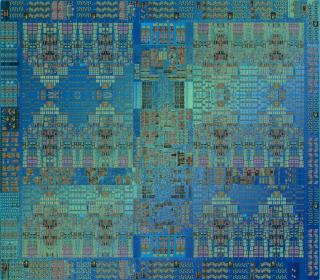

Intel launches its 3rd Generation Xeon Scalable, formerly Ice Lake. Fabricated on the company’s 10nm process, those server chips go up to 40 Sunny Cove cores and offer a 20% IPC improvement over the prior generation.

Read more