IEDM 2017 + ISSCC 2018: Intel’s 10nm, switching to cobalt interconnects

SRAM

Intel has scaled the SRAM at 0.62x for all the cells. The various cells are optimized for density, power, and performance. The high-density (PU:PG:PD = 1:1:1) cell has shrunk from 0.0499 squared micron down to 0.0312 while the high-performance (PU:PG:PD = 1:2:2) of 0.441 squared micron.

| Intel’s 10nm SRAM Cells | |||

|---|---|---|---|

| Cell | 14 nm | 10 nm | Scaling |

| High-Density | 0.0499 µm² | 0.0312 µm² | 0.63x |

| High-Performance | 0.0706 µm² | 0.0441 µm² | 0.63x |

| Low-Voltage | 0.0588 µm² | 0.0367 µm² | 0.63x |

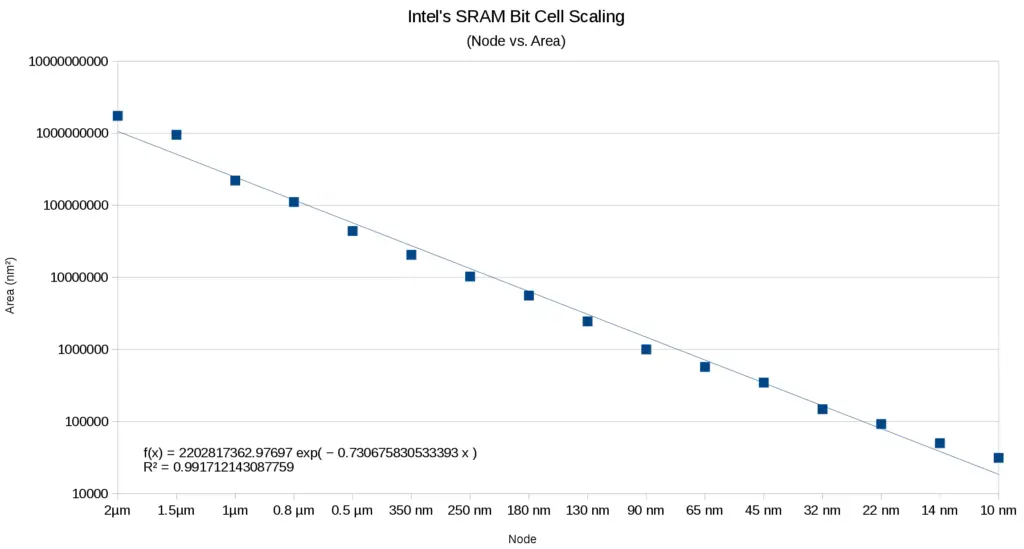

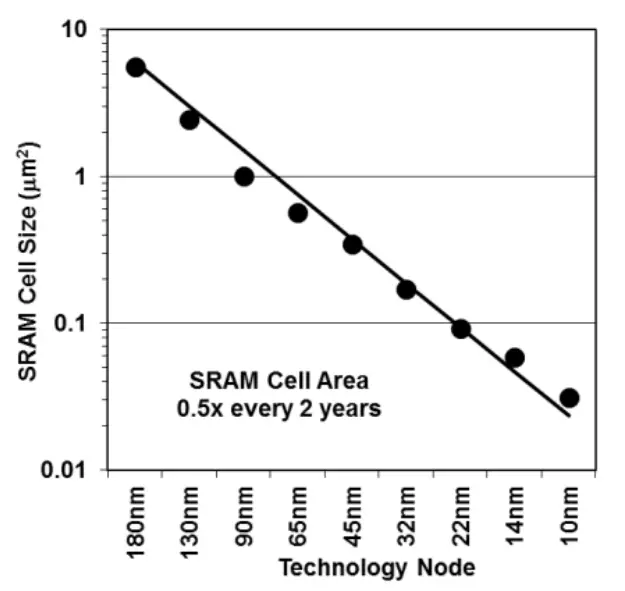

We have plotted Intel’s 10nm SRAM cell on the graph along with all of their historical SRAM cell sizes.

Despite still being on Moore’s doubling trend line, SRAM scaling has slowed down in recent nodes and has fallen behind. In fact Intel’s own 10nm paper also demonstrates that.

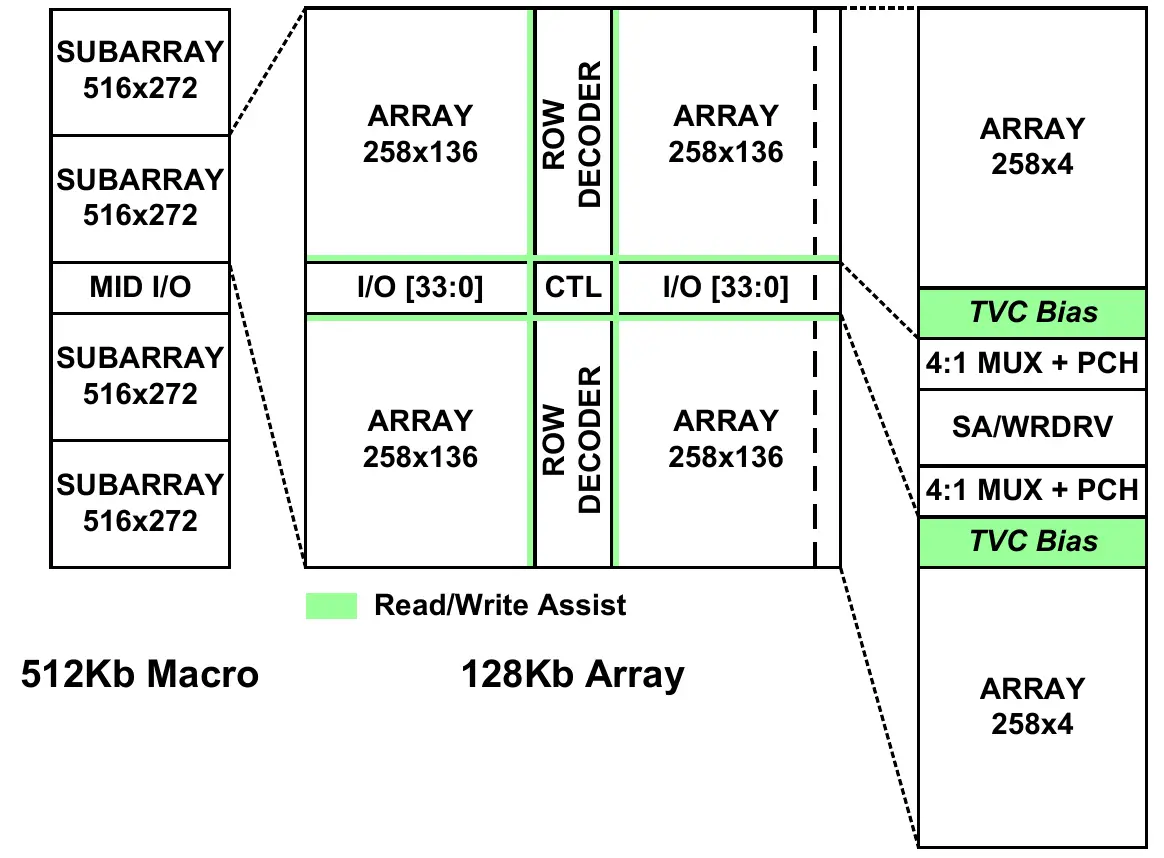

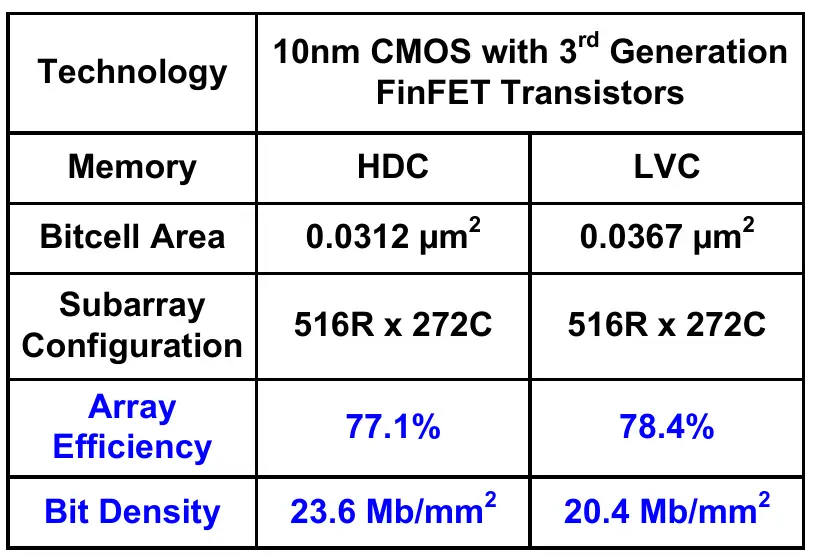

At the ISSCC 2018, Intel further detailed their SRAM array architecture.

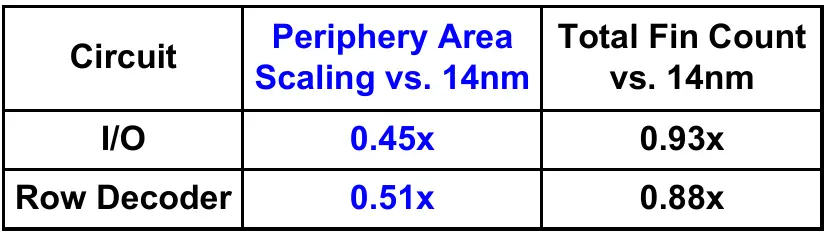

For their 10nm, Intel has significantly improved periphery area scaling resulting in double or better density improvement while having very little fin depopulation.

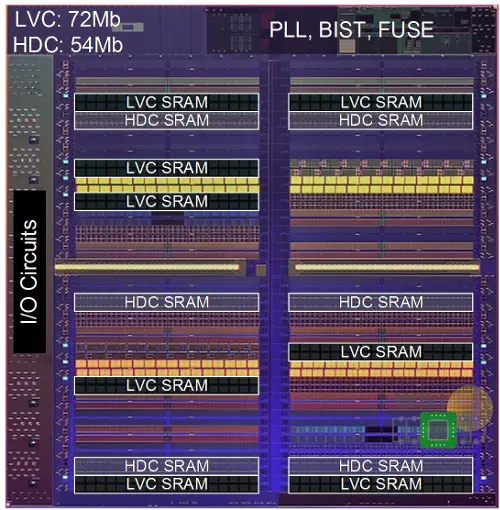

Test Shuttle

Intel’s 10nm test shuttle chip consisted of over 175 Mib of SRAM with at least 72 Mib of the low voltage cells and another 54 Mib of the high-density cells.

All in all, Intel has reported a bit density of 23.6 Mib/mm² and 20.4 Mib/mm² for the high-density and low-voltage cells respectively with around 78% array efficiency.

–

Spotted an error? Help us fix it! Simply select the problematic text and press Ctrl+Enter to notify us.

–