TSMC Announces 2x Reticle CoWoS For Next-Gen 5nm HPC Applications

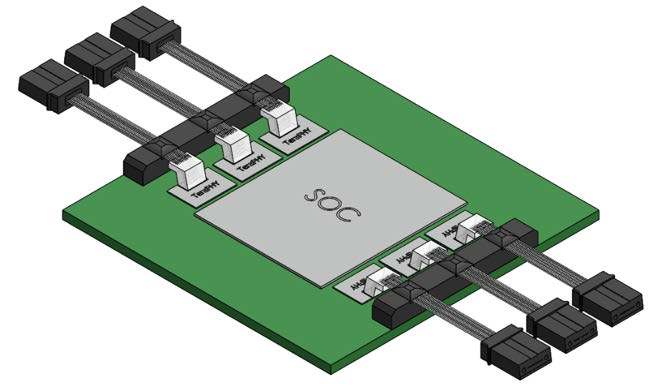

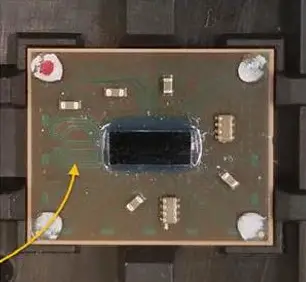

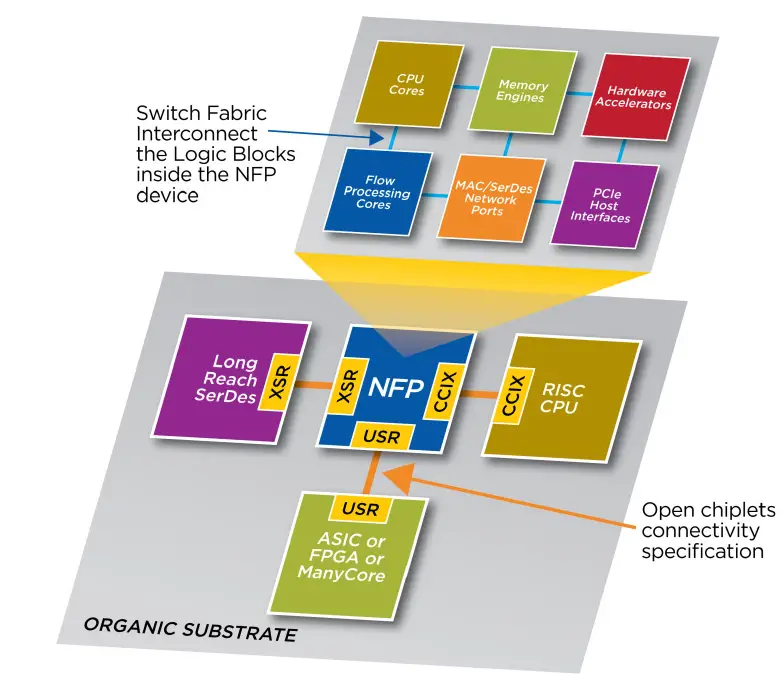

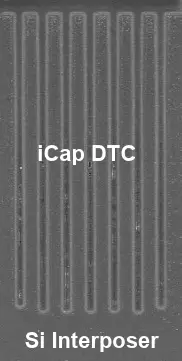

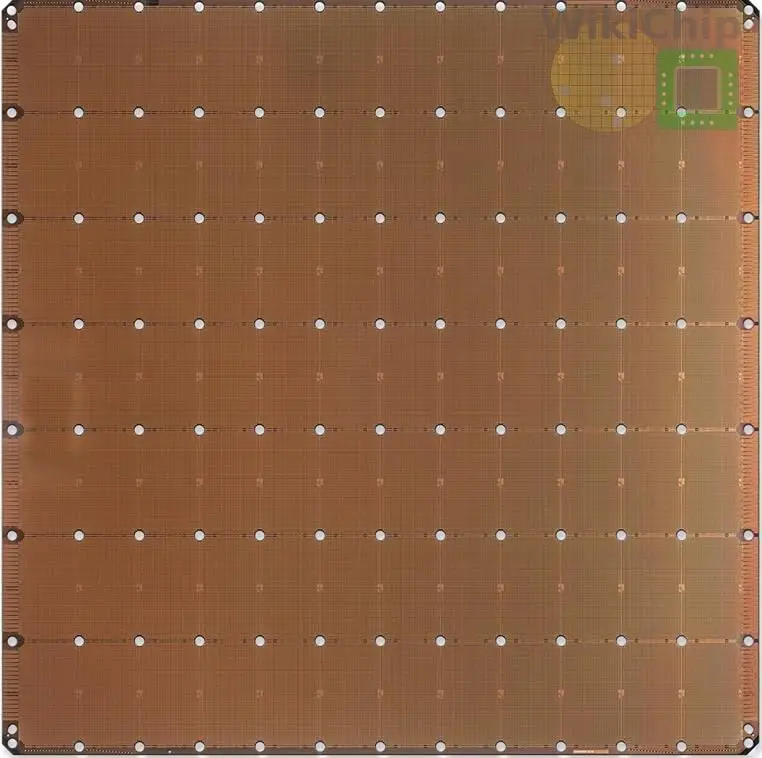

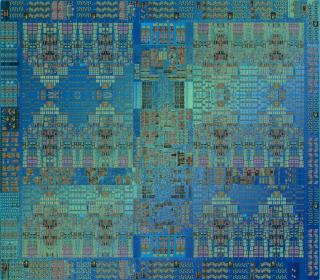

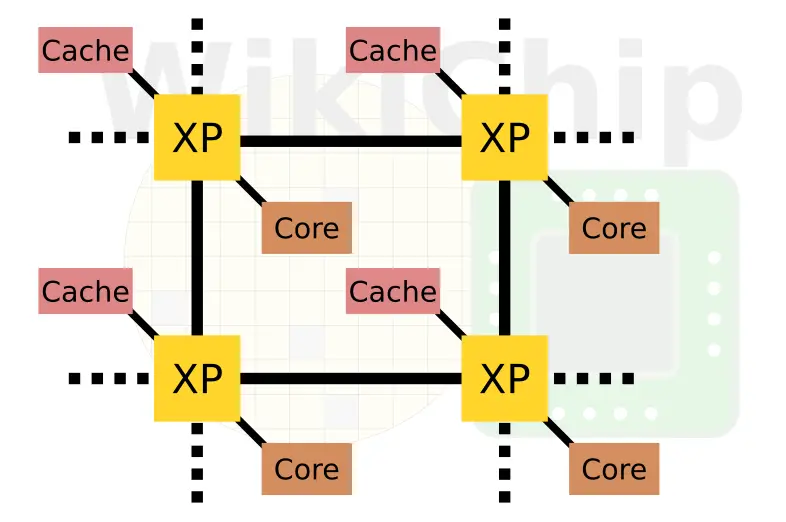

TSMC announces an enhancement to its CoWoS packaging technology with support for up to 2x the reticle size. The new technology is ready for next-generation 5-nanometer HPC applications.

Read more